# ANALOG LOW NOISE AMPLIFIER CIRCUIT DESIGN AND OPTIMIZATION

A Thesis submitted to Gujarat Technological University

for the Award of

## **Doctor of Philosophy**

in

# **Electronics & Communication Engineering**

by

# Hasmukh Pitambarbhai Koringa

[119997111005]

under supervision of

Dr. Vipul A Shah

# GUJARAT TECHNOLOGICAL UNIVERSITY AHMEDABAD

[May - 2017]

# ANALOG LOW NOISE AMPLIFIER CIRCUIT DESIGN AND OPTIMIZATION

A Thesis submitted to Gujarat Technological University

for the Award of

# **Doctor of Philosophy**

in

# **Electronics & Communication Engineering**

by

### Hasmukh Pitambarbhai Koringa

[119997111005]

under supervision of

Dr. Vipul A Shah

# GUJARAT TECHNOLOGICAL UNIVERSITY AHMEDABAD

[May - 2017]

© [Hasmukh Pitambarbhai Koringa]

**DECLARATION**

I declare that the thesis entitled Analog Low Noise Amplifier Circuit Design and

**Optimization** submitted by me for the degree of Doctor of Philosophy is the record of

research work carried out by me during the period from September 2011 to May 2017

under the supervision of Dr. Vipul A Shah and this has not formed the basis for the award

of any degree, diploma, associateship, fellowship, titles in this or any other University or

other institution of higher learning.

I further declare that the material obtained from other sources has been duly

acknowledged in the thesis. I shall be solely responsible for any plagiarism or other

irregularities, if noticed in the thesis.

Signature of Research Scholar:

Date: 10/05/2017

Name of Research Scholar: Hasmukh Pitambarbhai Koringa

Place: Ahmedabad

iii

**CERTIFICATE**

I certify that the work incorporated in the thesis Analog Low Noise Amplifier Circuit

Design and Optimization submitted by Shri Hasmukh Pitambarbhai Koringa was

carried out by the candidate under my supervision/guidance. To the best of my knowledge:

(i) the candidate has not submitted the same research work to any other institution for any

degree/diploma, Associateship, Fellowship or other similar titles (ii) the thesis submitted

is a record of original research work done by the Research Scholar during the period of

study under my supervision, and (iii) the thesis represents independent research work on

the part of the Research Scholar.

Signature of Supervisor:

Date: 10/05/2017

Name of Supervisor: Dr. Vipul A Shah

Place: Ahmedabad

iv

**Originality Report Certificate**

It is certified that PhD Thesis titled Analog Low Noise Amplifier Circuit Design and

Optimization submitted by Mr. Hasmukh Pitambarbhai Koringa has been examined

by us. We undertake the following:

a. Thesis has significant new work / knowledge as compared already published or are

under consideration to be published elsewhere. No sentence, equation, diagram,

table, paragraph or section has been copied verbatim from previous work unless it

is placed under quotation marks and duly referenced.

b. The work presented is original and own work of the author (i.e. there is no

plagiarism). No ideas, processes, results or words of others have been presented as

Author own work.

c. There is no fabrication of data or results which have been compiled / analysed.

d. There is no falsification by manipulating research materials, equipment or

processes, or changing or omitting data or results such that the research is not

accurately represented in the research record.

e. The thesis has been checked using https://turnitin.com (copy of originality report

attached) and found within limits as per GTU Plagiarism Policy and instructions

issued from time to time (i.e. permitted similarity index <=25%).

Signature of Research Scholar:

Date: 10/05/2017

Name of Research Scholar: Hasmukh Pitambarbhai Koringa

Place: Ahmedabad

Signature of Supervisor:

Date: 10/05/2017

Name of Supervisor: Dr. Vipul A Shah

Place: Ahmedabad

$\mathbf{v}$

# **Copy of Originality Report**

## Turnitin Originality Report

Processed on: 12-Sep-2016 15:06 IST

ID: 704098353 Word Count: 27025 Submitted: 1

Ph.D. Thesis by Hasmukh P Koringa By GCET 011

#### **Document Viewer**

Similarity Index

6%

Similarity by Source

Internet Sources: 2% Publications: 5% Student Papers: 1%

1% match (publications)

Koringa, Hasmukh P, Bhushan D. Joshi, and Vipul Shah. "High power gain low noise amplifier design for next generation 1–7GHz wideband RF frontend RFIC using 0.18µm CMOS", 2015 19th International Symposium on VLSI Design and Test, 2015.

1% match (publications)

Arshad, S., F. Zafar, R. Ramzan, and Q. Wahab. "Wideband and multiband CMOS LNAs: State-of-the-art and future prospects", Microelectronics Journal, 2013.

1% match (Internet from 24-May-2016)

$\frac{https://ecommons.usask.ca/bitstream/handle/10388/ETD-2013-12-1337/ZHANG-DISSERTATION.pdf?isAllowed=y\&sequence=4$

1% match (publications)

Galal, A.I.A.. "High linearity technique for ultra-wideband low noise amplifier in 0.18@mm CMOS technology", AEUE - International Journal of Electronics and Communications, 201201

1% match (Internet from 19-May-2010)

http://dspace.uta.edu

1% match (publications)

Koringa, Hasmukh P, and Vipul A Shah. "Design and optimization of narrow band low noise amplifier using 0.18µm CMOS", 2015

International Conference on Communication Networks (ICCN), 2015.

1% match (publications)

SpringerBriefs in Electrical and Computer Engineering, 2015.

# PhD THESIS Non-Exclusive License to GUJARAT TECHNOLOGICAL UNIVERSITY

In consideration of being a PhD Research Scholar at GTU and in the interests of the facilitation of research at GTU and elsewhere, I, **Hasmukh Pitambarbhai Koringa** having Enrollment No. **119997111005** hereby grant a non-exclusive, royalty free and perpetual license to GTU on the following terms:

- a) GTU is permitted to archive, reproduce and distribute my thesis, in whole or in part, and/or my abstract, in whole or in part (referred to collectively as the "Work") anywhere in the world, for non-commercial purposes, in all forms of media;

- b) GTU is permitted to authorize, sub-lease, sub-contract or procure any of the acts mentioned in paragraph (a);

- c) GTU is authorized to submit the Work at any National / International Library, under the authority of their "Thesis Non-Exclusive License";

- d) The Universal Copyright Notice (©) shall appear on all copies made under the authority of this license;

- e) I undertake to submit my thesis, through my University, to any Library and Archives. Any abstract submitted with the thesis will be considered to form part of the thesis.

- f) I represent that my thesis is my original work, does not infringe any rights of others, including privacy rights, and that I have the right to make the grant conferred by this non-exclusive license.

- g) If third party copyrighted material was included in my thesis for which, under the terms of the Copyright Act, written permission from the copyright owners is required, I have obtained such permission from the copyright owners to do the acts mentioned in paragraph (a) above for the full term of copyright protection.

- h) I retain copyright ownership and moral rights in my thesis, and may deal with the copyright in my thesis, in any way consistent with rights granted by me to my University in this non-exclusive license.

i) I further promise to inform any person to whom I may hereafter assign or license my

copyright in my thesis of the rights granted by me to my University in this non-

exclusive license.

j) I am aware of and agree to accept the conditions and regulations of PhD including all

policy matters related to authorship and plagiarism.

| Signature of Research Scholar: |  |

|--------------------------------|--|

|                                |  |

Name of Research Scholar: Hasmukh Pitambarbhai Koringa

Date: 10/05/2017 Place: Ahmedabad

| Signature of Supervisor: |  |

|--------------------------|--|

|--------------------------|--|

Name of Supervisor: **Dr. Vipul A Shah**

Date: 10/05/2017 Place: Ahmedabad

Seal:

# **Thesis Approval Form**

The viva-voce of the PhD Thesis submitted by Shri Hasmukh Pitambarbhai Koringa (En. No. 119997111005) entitled Analog Low Noise Amplifier Circuit Design and Optimization was conducted on 10/05/2017 (Wednesday) at Gujarat Technological University.

#### (Please tick any one of the following option)

The performance of the candidate was satisfactory. We recommend that he be awarded the Ph.D. Degree.

Any further modifications in research work recommended by the panel after 3 months from the date of first viva-voce upon request of the Supervisor after which viva-voce can be re-conducted by the same panel again.

| (briefly specify the modifications su        | aggested by the panel)                       |

|----------------------------------------------|----------------------------------------------|

| should not be awarded the Ph.D. De           |                                              |

| (The panel must give justifications          | for rejecting the research work)             |

| Name and Signature of Supervisor with Seal   | 1) (External Examiner -1) Name and Signature |

| 2) (External Examiner -2) Name and Signature | 3) (External Examiner -3) Name and Signature |

#### **ABSTRACT**

The design of RF frontend for the next generation wireless communication is one of the emerging areas of research in field of RFIC. In 2002 Federal Communication Committee (FCC) had released 3.1 - 10.6 GHz Ultra Wideband (UWB) for commercial purpose with two restriction, low power transmission (Emission Isotropic Radiated Power must be lower then -41.3 dBm/MHz) and 500 MHz minimum bandwidth. These restrictions put stringent requirements on designing of UWB receiver. Overall sensitivity and noise figure of receiver is dominated by the first amplifier block of receiver known as Low Noise Amplifier (LNA). Due to very large 7.5 GHz wide bandwidth UWB technology has desirable features such as less multipath fading, good range and time resolution, high data rate and easier material penetration. The UWB technology is widely use in image penetration, high data rate short distance wireless communication, high accuracy locating and positioning and medical applications. Most challenging task in implementation of UWB technology is to design LNA for UWB receiver. Realization of UWB receiver requires wideband matching, high power gain, low noise figure and good linearity LNA.

In this thesis proposed design of 3.1 - 10.6 GHz wideband high power gain Low Noise Amplifier for UWB receiver. Common Gate (CG) configuration of amplifier is used in the first stage of UWB LNA design for wideband input impedance matching. Input impedance and Noise Figure (NF) of the CG are analyzed and optimized to improve performance of the LNA. The gain of design is improved by using cascode Common Source (CS) stages after CG. NF and power gain of the design are improved by using inductive load in each stage. Overall wideband high flat gain is achieved by resonate each stage parallel tune circuit at different frequencies of interested band. This novel multistage UWB LNA design provides very high power gain, low noise figure, wideband input impedance matching and good linearity in interested 3.1 – 10.6 GHz wideband.

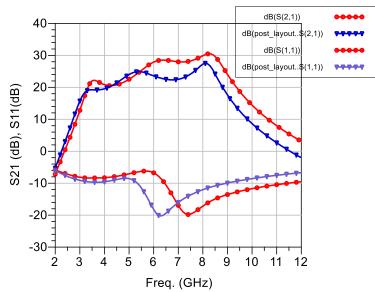

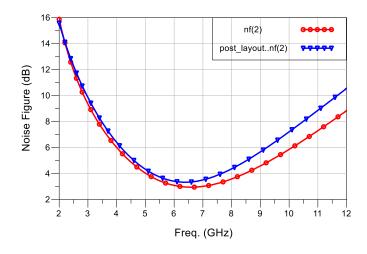

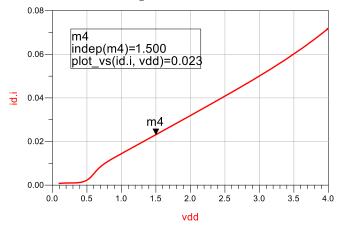

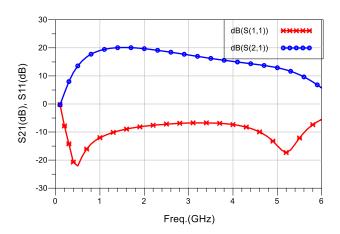

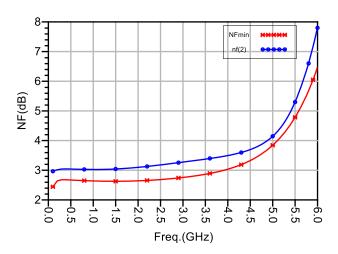

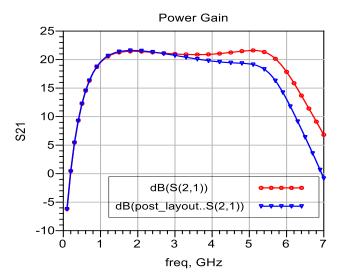

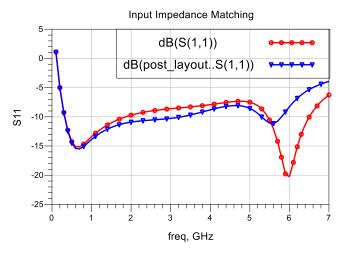

Simulated results shows the proposed high power gain UWB LNA design has 20-30 dB power gain and 2.8-6 dB NF in interested band. The design achieved input impedance match (S<sub>11</sub>) and linearity measure IIP3 are -9 dB and -5.5 dBm respectively. The UWB LNA is consume 34 mW power from 1.5 V supply. Due to high power gain, good linearity, low noise figure and wideband matching of the proposed UWB LNA will

improve performance of the future UWB receiver and it will open new frontier for UWB wireless communication users.

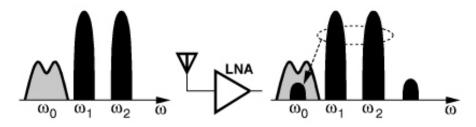

In the day to day life wireless communication applications are increasing. Wireless communication users demand modern mobile terminal should support GSM, UMTS, CDMA, GPS, RFID, Bluetooth, ZigBee, WLAN, LTE, WiMax, etc. different wireless communication standards of 2G, 3G and upcoming 4G technologies. Recently have been observing a paradigm shift in the integrated wireless transceiver design where several narrowband receivers which customized for dedicated applications are replaced by one single receiver which supports different standards operating on different frequencies band. Implementation of the LNA for multi standards receiver is most critical task. Performance of the LNA determines the overall receiver noise figure and sensitivity.

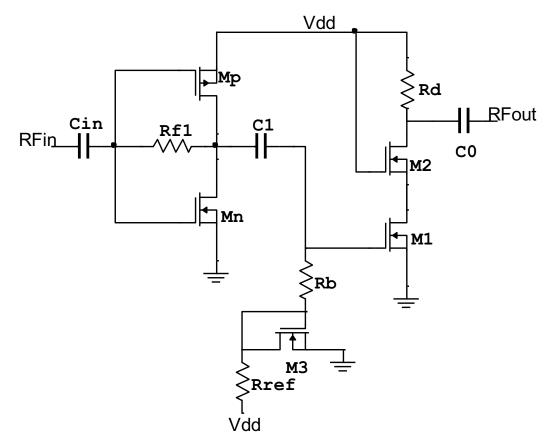

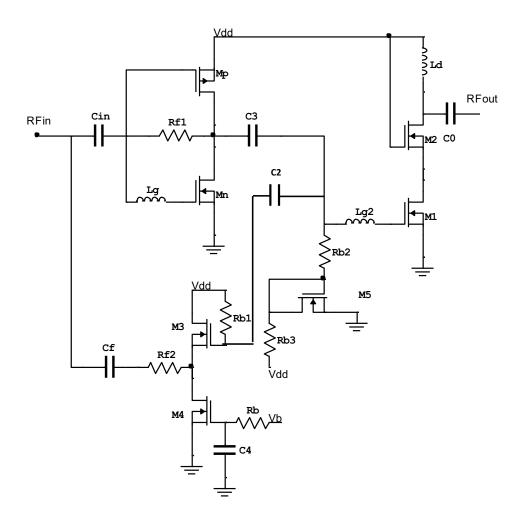

When strong interference signals are received with weak desire signals require highly linear receiver design to avoid blocking. The proposed next design is for highly linear 0.6-5.6 GHz wideband LNA for future multi standards universal receiver. Current reuse NMOS/PMOS inverter structure of amplifier is providing high linearity by cancelling distortion due to complementary characteristics of NMOS and PMOS transistors. Detail analysis of noise figure and input impedance shows resistive feedback inverter LNA topology has tradeoff between NF and matching. The proposed resistive and CD feedback NMOS/PMOS inverter structure design is relax the tradeoff by providing one more degree of freedom to set NF and matching independently. Analysis of CD feedback shows that it is not only relax tradeoff but also reduce noise by cancelling out off phase noise signals. Inductive series and shunt peaking cascode CS amplifier next stage is used with resistive and CD feedback inverter structure first stage to improve overall gain and bandwidth of the design.

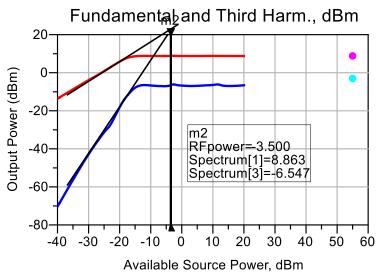

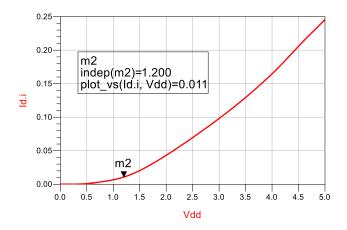

Proposed highly linear wideband LNA design is simulated using 0.18  $\mu$ m RFCMOS MOSFET model. This design achieved very good linearity average IIP3 is + 4 dBm in 0.6-5.6 GHz interested band. Other performance parameters of the LNA, power gain (S<sub>21</sub>), NF and S<sub>11</sub> are 20 dB, <4 dB and <-9 dB respectively in 0.6-5.6 GHz wideband. This design is consuming only 13.2 mW power from 1.2 V supply. Results shows the design is highly suitable for implementation of future universal receiver to support GSM, UMTS, CDMA, Bluetooth, ZigBee, RFID, WLAN, LTE, WiMAX, etc. wireless communication

standards. Third high power gain multi standard wideband LNA design is proposed for very high power gain base station universal receiver.

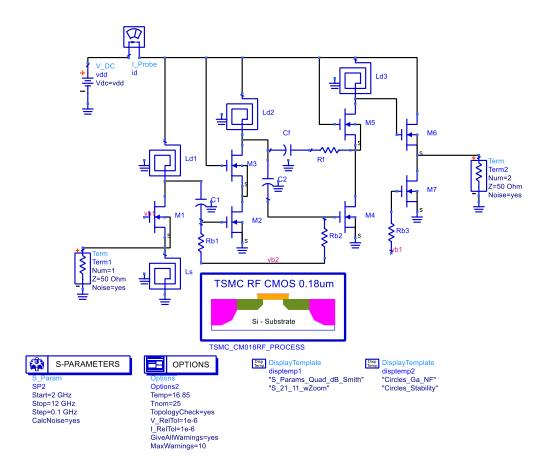

All the LNAs have been designed using TSMC 0.18 µm RFCMOS technology and simulate the designs using Advanced Design System (ADS) RF circuit simulator. These wideband LNA designs are proposed for the next generation wireless receiver implementation. The performance tradeoff among input matching, noise figure, gain and linearity are analyzed in detail and in the research proposed novel circuit techniques for to relax performance tradeoff. The results indicate that the proposed LNAs design will improve performance of the next generation wireless communication.

# Acknowledgment

This thesis would have been impossible without support of many people. I would like to express my sincere gratitude to them, though their invaluable support deserves much more than this short note of appreciation. I would like to thanks Almighty the God giving me strength and passion to do research.

I would like to express my sincere appreciation to my supervisor **Dr. Vipul A Shah** for his valuable enthusiastic guidance and encouragement me during every steps of my research. Due to his extensive technical support able complete my research in time. I wholeheartedly give my best wishes to him and his family. I would like to express my sincere gratitude to my co-supervisor **Prof. Durgamadhab Misra** for his valuable technical support.

Also, I would like to express my sincere gratitude to **Dr. Mihir V Shah** and **Dr. Ramji Makwana**. It was great honour to have them as my thesis Doctoral Progress Committee member. Their constructive suggestions made the thesis sound in many aspects.

I would like sincere thanks to **Mr. Bhushan Joshi** for supporting me to learn ADS RF circuit simulation tool. I would like to express my gratitude to **Dr. C. H. Vithalani** and EC department GCET for supporting me whenever needed.

I also acknowledge Honourable Vice Chancellor, Registrar, Controller of Examination, Dean Ph.D. section and all staff members of Ph.D. section of university for their assistance and support.

I would like to express my sincere appreciation to my Ph.D. thesis examiners who have speared his valuable time to evaluate thesis.

Finally, I give the greatest respect and love to my parents, my parents in law, my wife and my son **Manas**. I want to express my highest appreciation for their support and cooperation. I would like to say thanks to my wife **Mrs. Miral** for encourage me to do research and her moral support. Thanks to **Almighty the God** for given me patient to complete research.

This thesis is dedicated to all of my good wisher with my love for assisting me to achieve the most important stage in my life. I will never let them down and wish them all the successes in the future.

# **Table of Contents**

|    | Abstract       |                                                    | X     |

|----|----------------|----------------------------------------------------|-------|

|    | Acknowledge    | ment                                               | xiii  |

|    | Table of Cont  | tents                                              | XV    |

|    | List of Abbre  | viations                                           | xviii |

|    | List of Symbo  | bls                                                | XX    |

|    | List of Figure | s                                                  | xxi   |

|    | List of Tables | 3                                                  | xxvi  |

| 1. | Introduction   |                                                    | 1     |

|    | 1.1 Introd     | uction                                             | 1     |

|    | 1.2 Unive      | rsal Receiver                                      | 2     |

|    | 1.3 Introd     | uction of UWB system                               | 3     |

|    | 1.4 The C      | MOS Technology                                     | 4     |

|    | 1.5 Defini     | ition of the Problem                               | 4     |

|    | 1.6 Object     | tive and Scope of the Work                         | 5     |

|    | 1.7 Origin     | nal Contribution of the Thesis                     | 5     |

|    | 1.8 Thesis     | s Organization                                     | 7     |

| 2. | LNA Fundar     | nentals                                            | 9     |

|    | 2.1 S Para     | ameters                                            | 9     |

|    | 2.2 Low N      | Noise Amplifier (LNA) Performance Parameters       | 11    |

|    | 2.2.1          | Noise Performance                                  | 11    |

|    | 2.2.2          | Power Gain and Impedance Matching                  | 15    |

|    | 2.2.3          | Linearity                                          | 15    |

|    | 2.2.4          | Power Consumption                                  | 20    |

|    | 2.2.5          | Stability                                          | 20    |

| 3. | Literature R   | eview                                              | 22    |

|    | 3.1 Widel      | oand LNA Implementation Approaches                 | 22    |

|    | 3.2 Comn       | non Source with Resistive Termination LNA Topology | 23    |

|    | 3.3 Comm       | non Gate Topology                                  | 25    |

|    | 3.3.1          | Noise Figure Analysis of CG                        | 25    |

|    | 3.4 Feedb      | ack LNA Topologies                                 | 27    |

|    | 3.4.1          | Resistive Feedback LNA Topology                    | 28    |

|    | 3.4.2       | Reactive Feedback LNA Topology                    | 31 |

|----|-------------|---------------------------------------------------|----|

|    | 3.4.3       | Active Feedback LNA Topology                      | 32 |

|    | 3.5 Filter  | LNA Topology                                      | 32 |

|    | 3.6 Distrib | outed Amplifier LNA Topology                      | 33 |

| 4. | Narrowband  | LNAs Design and Optimization                      | 37 |

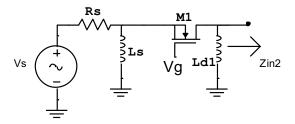

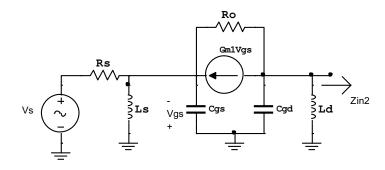

|    | 4.1 Induct  | ive Degenerate Common Source (IDCS) LNA Topology  | 37 |

|    | 4.1.1       | Input Impedance Analysis                          | 38 |

|    | 4.1.2       | Gain Analysis                                     | 39 |

|    | 4.1.3       | Noise Performance Analysis                        | 41 |

|    | 4.2 Bias C  | Circuit Design                                    | 43 |

|    | 4.3 Blueto  | ooth Receiver LNA Design using IDCS Topology      | 46 |

|    | 4.3.1       | LNA Specifications for Bluetooth Receiver         | 46 |

|    | 4.3.2       | LNA Design Steps                                  | 48 |

|    | 4.3.3       | Schematic of the Bluetooth IDCS LNA               | 50 |

|    | 4.3.4       | Design Optimization                               | 51 |

|    | 4.3.5       | Simulation Results and Discussion                 | 54 |

|    | 4.4 Blueto  | ooth Receiver LNA Design using Current Reuse (CR) |    |

|    | Topol       | ogy                                               | 57 |

|    | 4.4.1       | Bluetooth CRLNA Schematic                         | 57 |

|    | 4.4.2       | Simulation Results and Discussion                 | 59 |

|    | 4.5 GPS F   | Receiver LNA Design                               | 62 |

|    | 4.5.1       | GPS Receiver LNA Design using IDCS topology       | 62 |

|    | 4.5.2       | Simulation Results and Discussion of GPS IDCS LNA | 63 |

|    | 4.5.3       | GPS Receiver LNA Design using CR topology         | 65 |

|    | 4.5.4       | Simulation Results and Discussion of GPS CRLNA    | 68 |

| 5. | High Power  | Gain UWB LNA                                      | 72 |

|    | 5.1 Introd  | uction                                            | 72 |

|    | 5.1.1       | Ultra Wide Band (UWB) Technology                  | 72 |

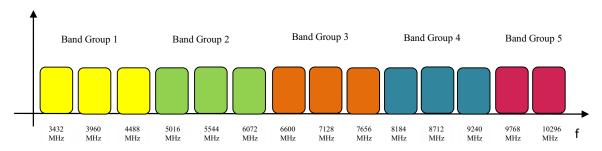

|    | 5.1.2       | Bandwidth and Guidelines of UWB Technology        | 73 |

|    | 5.1.3       | Features and Applications of UWB Technology       | 73 |

|    | 5.1.4       | UWB System Standards                              | 74 |

|    | 5.1.5       | UWB System Architectures                          | 74 |

|    | 5.2 Propos  | sed High Power Gain UWB LNA                       | 77 |

|    | 5.2.1       | Circuit Analysis of the Proposed Design           | 78 |

|    | 5.2.2         | Input Impedance Analysis                       | 79  |

|----|---------------|------------------------------------------------|-----|

|    | 5.2.3         | Noise Analysis and Optimization                | 80  |

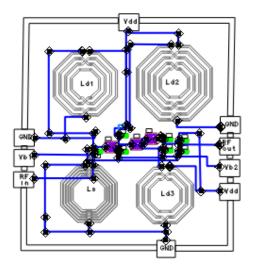

|    | 5.2.4         | Layout of UWB LNA Design                       | 81  |

|    | 5.2.5         | Simulation Results and Discussion              | 82  |

| 6. | Multi Star    | ndard Wideband LNAs                            | 87  |

|    | 6.1 Introd    | uction                                         | 87  |

|    | 6.2 NMO       | S/PMOS Inverter structure Amplifier            | 88  |

|    | 6.2.1         | Linearity Analysis                             | 89  |

|    | 6.3 Resist    | ive Feedback Inverter Wideband LNA             | 90  |

|    | 6.3.1         | Input Impedance Analysis                       | 91  |

|    | 6.3.2         | Voltage Gain and Noise Figure Analysis         | 91  |

|    | 6.3.3         | Simulation Results and Discussion              | 92  |

|    | 6.4 Resis     | tive Feedback Inverter with Gate Inductor Lg   |     |

|    | Wide          | band LNA                                       | 95  |

|    | 6.4.1         | Circuit Analysis                               | 95  |

|    | 6.4.2         | Simulation Results and Discussion              | 98  |

|    | 6.4.3         | Comparison of with and without Lg LNA Design   | 99  |

|    | 6.5 Resis     | tive and CD Feedback Inverter Wideband LNA     | 99  |

|    | 6.5.1         | Common Drain (CD) Feedback Analysis            | 101 |

|    | 6.5.2         | Simulation Results and Discussion              | 102 |

|    | 6.6 Propo     | osed Highly Linear Multi Standard Wideband LNA | 103 |

|    | 6.6.1         | Design Analysis                                | 103 |

|    | 6.6.2         | Layout of Design                               | 105 |

|    | 6.6.3         | Simulation Results and Discussion              | 106 |

|    | 6.7 High      | Power Gain Wideband LNA                        | 108 |

|    | 6.7.1         | Proposed LNA Schematic                         | 108 |

|    | 6.7.2         | Layout of the Design                           | 109 |

|    | 6.7.3         | Simulation Results                             | 110 |

| 7. | Conclusio     | ns, Major Contributions, Scope of Further Work | 115 |

|    | 7.1 Concl     | usions and Major Contributions                 | 115 |

|    | 7.2 Scope     | of Further Work                                | 117 |

| L  | ist of Refer  | ences                                          | 119 |

| L  | ist of Biblio | graphy                                         | 125 |

| L  | ist of Publi  | cations                                        | 126 |

#### List of Abbreviations

ADC Analog-to-Digital Conversion

ADS Advanced Design System

AGC Automatic Gain Control

BPF Band Pass Filter

BW Bandwidth

CDMA Code Division Multiple Access

CG Common Gate

CMOS Complementary Metal Oxide Semiconductor

CS Common Source

CD Common Drain

CP Carrier Phase

CRLNA Current Reuse Low Noise Amplifier

DA Distributed Amplifier

DC Direct Current

DCS Digital Cellular Service

DSP Digital Signal Processing

EIRP Equivalent Isotropic Radiated Power

FB Feedback

FCC Federal Communication Commission

FFT Fast Fourier Transform

FOM Figure of Merit

GPS Global Positioning System

GSM Global System for Mobile Communications

HPF High Pass Filter

HSPA High Speed Packet Access

IC Integrate Circuit

ID Inductive Degenerate

IEEE Institute of Electrical and Electronics Engineering

IIP3 Third order Input Interception Point

IMT International Mobile Telecommunication Advanced

IR Impulse Radio

ITU International Telecommunication Union

KCL Kirchhoff Current Law

KVL Kirchhoff Voltage Law

LAN Local Area Network

LC Local Oscillator

LNA Low Noise Amplifier

LPF Low Pass Filter

LTE Long Term Evolution

MB OFDM Multi Band Orthogonal Frequency Division Multiple Access

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NF Noise Figure

NMOS N Channel Metal Oxide Semiconductor

OFDM Orthogonal Frequency Division Multiple Access

OIP Output Intercept Point

PAN Personal Area Network

PAM Pulse Amplitude Modulation

PCS Personal Communication Service

PMOS P channel Metal Oxide Semiconductor

PPM Pulse Position Modulation

PVT Process Voltage Temperature

RADAR Radio Detection And Ranging

RF Radio Frequency

RFIC Radio Frequency Integrated Circuit

RFID Radio Frequency Identification

SNR Signal-to-Noise Ratio

TSMC Taiwan Semiconductor manufacturing Company

UMTS Universal Mobile Telecommunication System

UWB Ultra Wideband

VGA Variable Gain Adjustment

VLSI Very Large Scale Integration

WCDMA Wideband Code Division Multiple Access

WiMAX Worldwide Interoperability for Microwave Access

WLAN WiFi Local Area Network

WPAN Wideband Personal Area Network

# **List of Symbols**

μm Micrometer

nm Nanometer

GHz Giga Hertz

K Boltsman constant

T Temperature

Δf Bandwidth

g<sub>m</sub> Transconductance

W Width of Channel

L Length of Channel

Cox Oxide Capacitance

Si Silicon Substrate

Sio2 Silicon Oxide

dB Decibel

$\Omega$  Ohm

KΩ Kilo Ohm

pF Pico Farad

fF Facto Farad

nH Nano Henri

MHz Mega Hertz

V Volt

mA Milli Ampere

Q Quality Factor

# **List of Figures**

| Figure 1.1  | Ideal universal radio architecture                                   | 2  |

|-------------|----------------------------------------------------------------------|----|

| Figure 1.2  | Practical universal radio architecture                               | 2  |

| Figure 2.1  | Two port network                                                     | 9  |

| Figure 2.2  | MOSFET channel thermal noise representation.                         | 13 |

| Figure 2.3  | Equivalent noise model for gate resistance.                          | 13 |

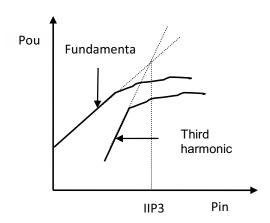

| Figure 2.4  | 1dB compression point                                                | 17 |

| Figure 2.5  | Cross modulation nonlinearity effect                                 | 18 |

| Figure 2.6  | Third order intermodulation nonlinearity effect                      | 19 |

| Figure 2.7  | Intermodulation Product                                              | 19 |

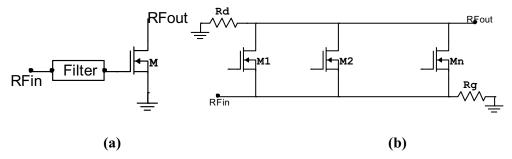

| Figure 3.1  | a) Resistive termination, b) common gate, c) feedback                | 22 |

| Figure 3.2  | a) filter and b) Distributed                                         | 23 |

| Figure 3.3  | Common Source (CS) with resistive termination topology               | 23 |

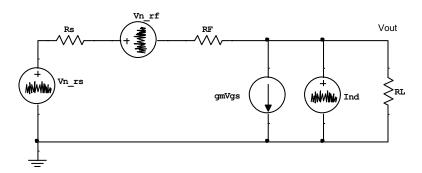

| Figure 3.4  | AC equivalent circuit with noise sources of resistive termination CS | 23 |

| Figure 3.5  | Common Gate (CG) topology                                            | 25 |

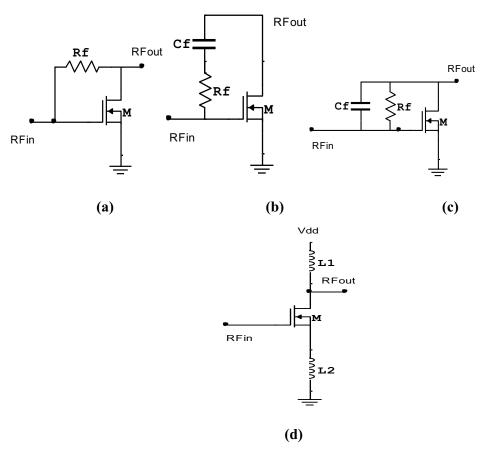

| Figure 3.6  | Feedback topology a) resistive b) series RC c) parallel RC and d)    |    |

|             | transformer                                                          | 27 |

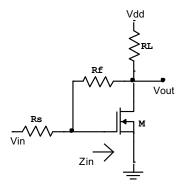

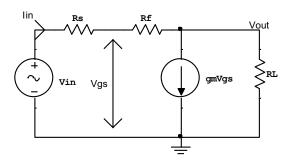

| Figure 3.7  | Resistive Feedback Common Source (CS) topology                       | 28 |

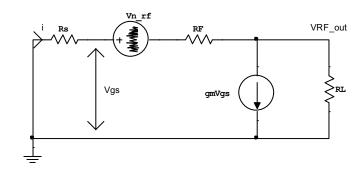

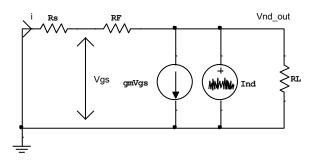

| Figure 3.8  | AC equivalent circuit of resistive feedback CS topology              | 28 |

| Figure 3.9  | AC equivalent circuit with noise sources of resistive feedback CS    | 29 |

| Figure 3.10 | Feedback resistance noise of resistive feedback CS                   | 30 |

| Figure 3.11 | MOSFET drain current noise circuit                                   | 30 |

| Figure 3.12 | Cascode DA Schematic                                                 | 34 |

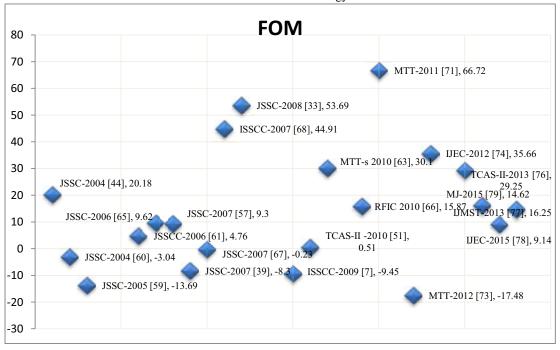

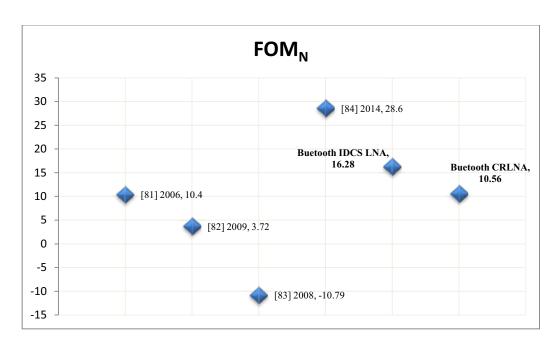

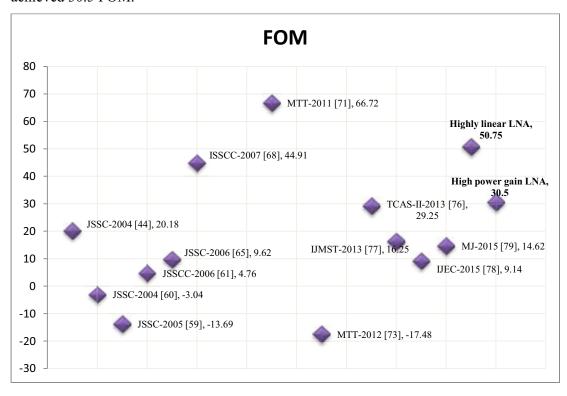

| Figure 3.13 | FOM of different LNAs design.                                        | 36 |

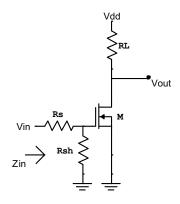

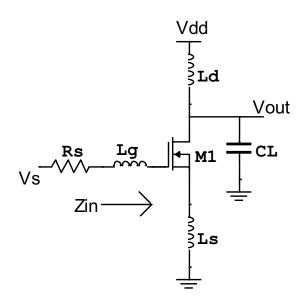

| Figure 4.1  | Inductive Degenerate Common Source LNA topology                      | 38 |

| Figure 4.2  | Inductive degenerate common source AC equivalent circuit             | 38 |

| Figure 4.3  | Input equivalent circuit of xxinductive source degenerate CS LNA     | 40 |

| Figure 4.4  | Inductive Load inductive source degenerate CS LNA                    | 42 |

| Figure 4.5  | Cascode ID common source LNA                                         | 43 |

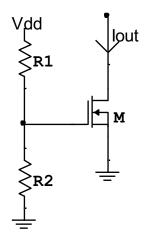

| Figure 4.6  | Resistive bias circuit                                               | 43 |

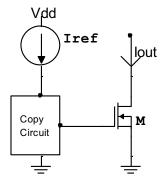

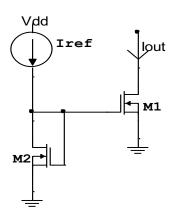

| Figure 4.7  | Current copying bias                                                 | 44 |

| Figure 4.8  | Current Mirror bias circuit                                          | 44 |

| Figure 4.9  | Inductive degenerate common source LNA topology with current           |    |

|-------------|------------------------------------------------------------------------|----|

|             | mirror bias                                                            | 45 |

| Figure 4.10 | Bluetooth Inductive degenerate common source LNA design                |    |

|             | schematic                                                              | 50 |

| Figure 4.11 | Performance tradeoff of LNA                                            | 51 |

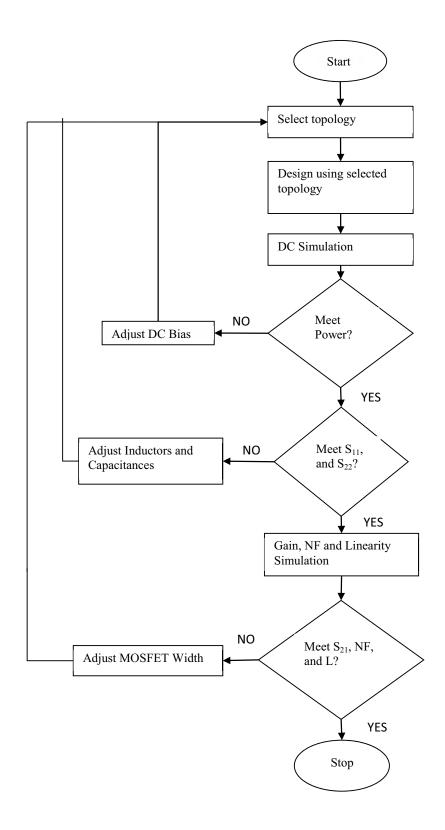

| Figure 4.12 | LNA Design flow chart                                                  | 52 |

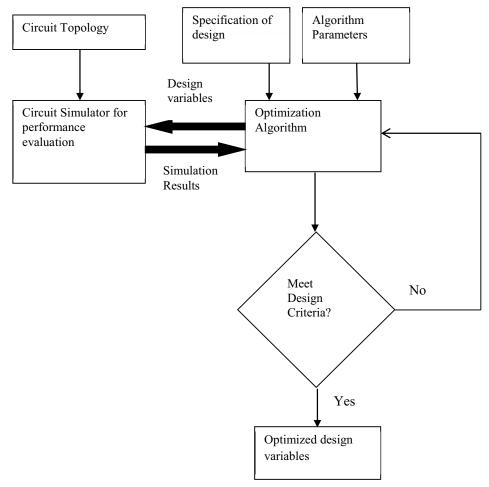

| Figure 4.13 | Optimization Flow Chart                                                | 53 |

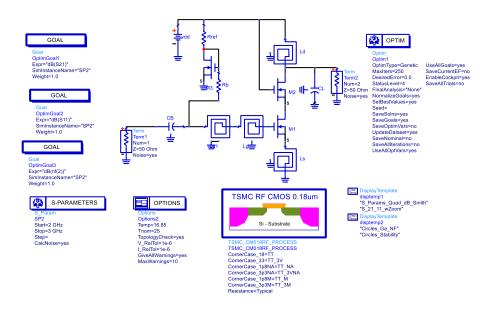

| Figure 4.14 | IDCS Bluetooth LNA ADS simulation schematic and optimization           |    |

|             | setup.                                                                 | 53 |

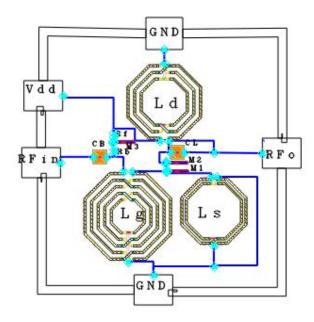

| Figure 4.15 | Layout of IDCS Bluetooth LNA.                                          | 54 |

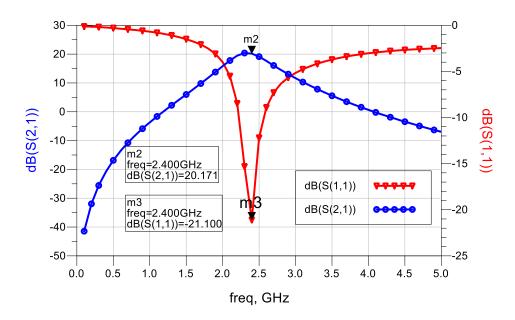

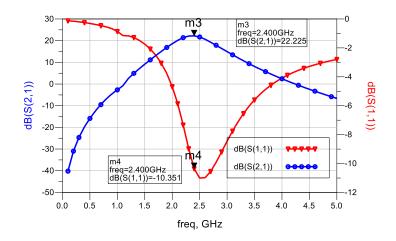

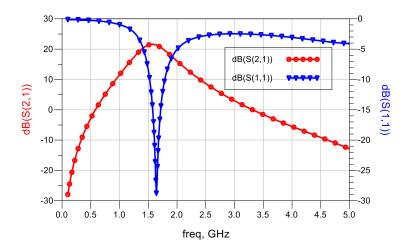

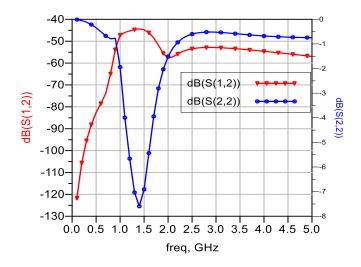

| Figure 4.16 | $S_{21}$ and $S_{11}$ Simulation results of Bluetooth LNA              | 54 |

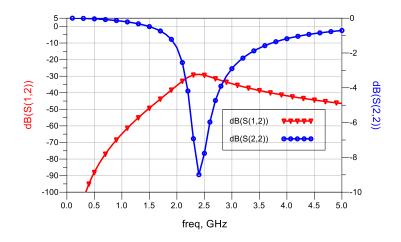

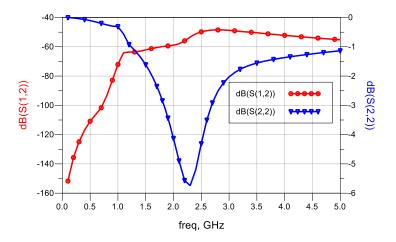

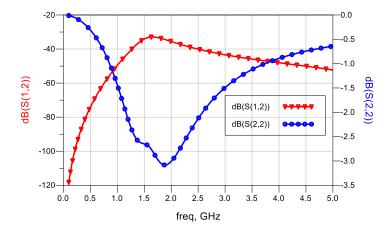

| Figure 4.17 | $S_{12}$ and $S_{22}$ Simulation results of Bluetooth LNA              | 55 |

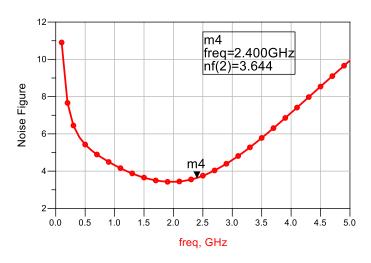

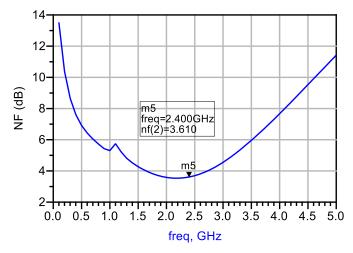

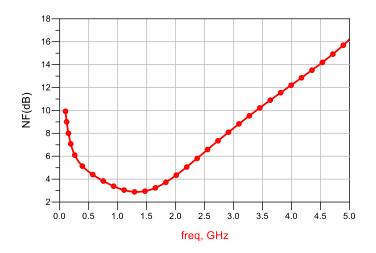

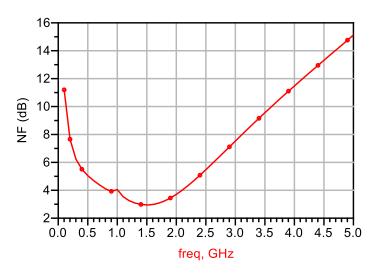

| Figure 4.18 | Noise Figure Simulation result of Bluetooth LNA                        | 55 |

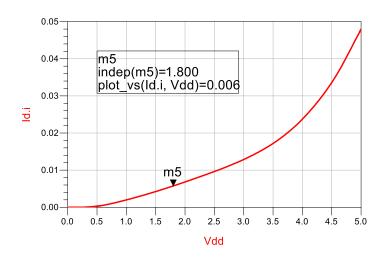

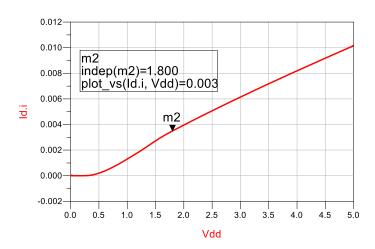

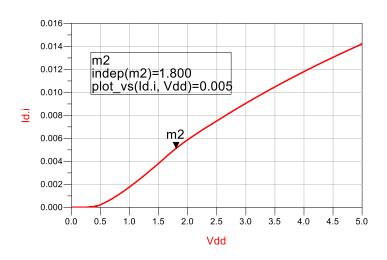

| Figure 4.19 | DC Simulation result Bluetooth LNA                                     | 55 |

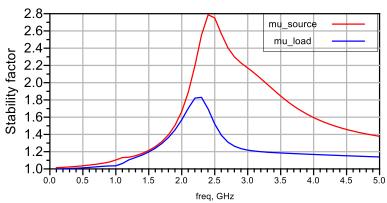

| Figure 4.20 | Stability factor simulation of Bluetooth LNA                           | 56 |

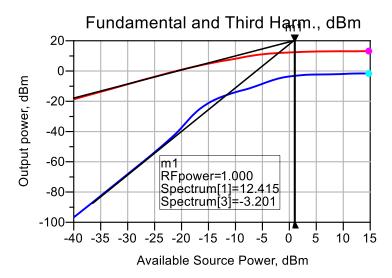

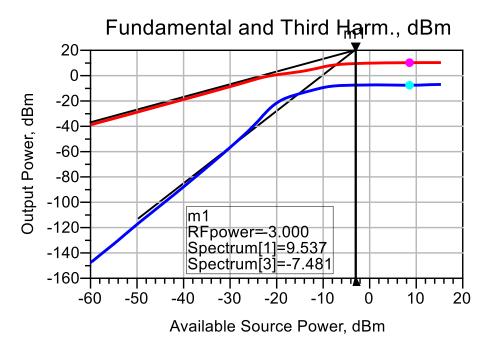

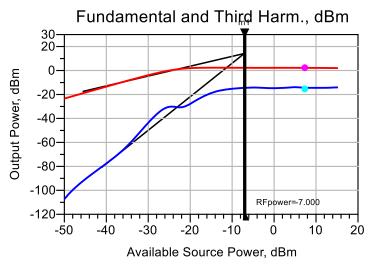

| Figure 4.21 | Harmonic simulation of Bluetooth LNA                                   | 56 |

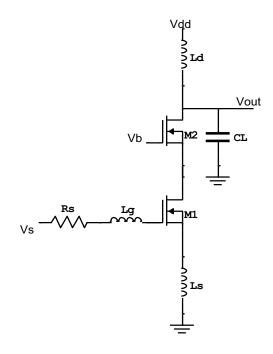

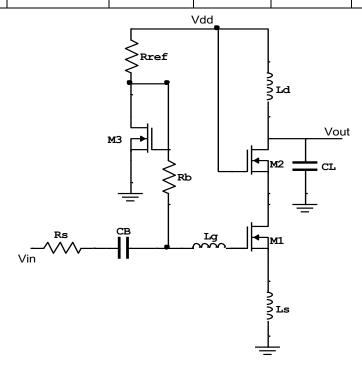

| Figure 4.22 | Inductive degenerate Current Reuse LNA (CRLNA) Schematic               | 58 |

| Figure 4.23 | Layout of Bluetooth CRLNA                                              | 58 |

| Figure 4.24 | S <sub>21</sub> and S <sub>11</sub> simulation results of CRLNA        | 59 |

| Figure 4.25 | S <sub>12</sub> and S <sub>22</sub> Simulation results of CRLNA        | 59 |

| Figure 4.26 | DC simulation of CRLNA                                                 | 59 |

| Figure 4.27 | Noise Figure Simulation results of CRLNA                               | 60 |

| Figure 4.28 | Harmonic Simulation of CRLNA                                           | 60 |

| Figure 4.29 | Stability factor simulation of CRLNA                                   | 60 |

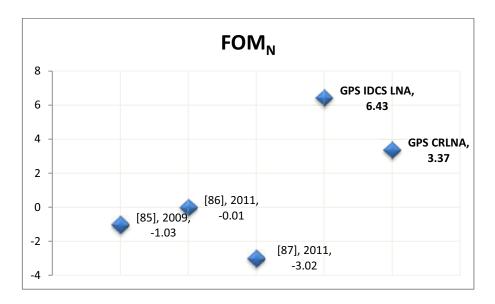

| Figure 4.30 | FOM of Published and proposed Bluetooth LNAs design                    | 61 |

| Figure 4.31 | GPS IDCS LNA schematic                                                 | 62 |

| Figure 4.32 | Layout of IDCS GPS LNA.                                                | 63 |

| Figure 4.33 | S <sub>21</sub> and S <sub>11</sub> simulation results of GPS IDCS LNA | 63 |

| Figure 4.34 | S <sub>12</sub> and S <sub>22</sub> simulation results of GPS IDCS LNA | 64 |

| Figure 4.35 | Noise Figure simulation results of GPS IDCS LNA                        | 64 |

| Figure 4.36 | DC Simulation of GPS IDCS LNA                                          | 64 |

| Figure 4.37 | Harmonic simulation of GPS IDCS LNA                                    | 65 |

| Figure 4.38 | GPS Current Reuse LNA (CRLNA) Schematic.                               | 65 |

| Figure 4.39 | CRLNA GPS LNA ADS simulator schematic.                                              | 66 |

|-------------|-------------------------------------------------------------------------------------|----|

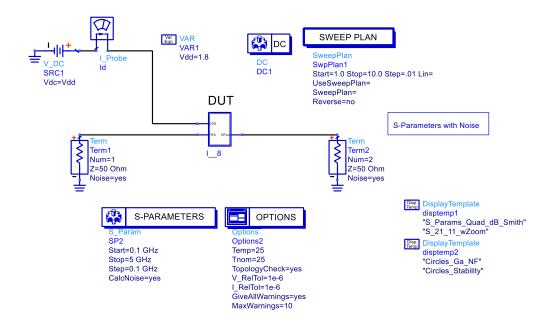

| Figure 4.40 | S parameters and Noise Performance simulation setup                                 | 67 |

| Figure 4.41 | Harmonics balance simulation setup.                                                 | 67 |

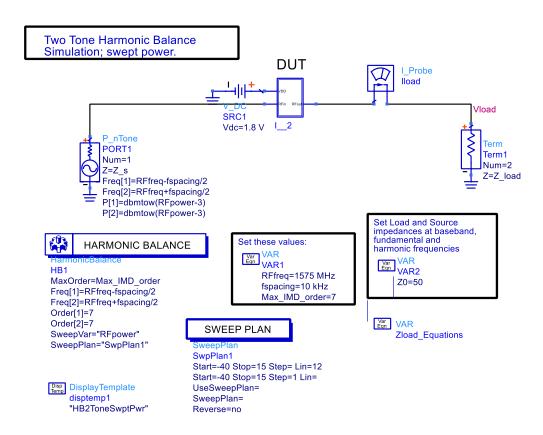

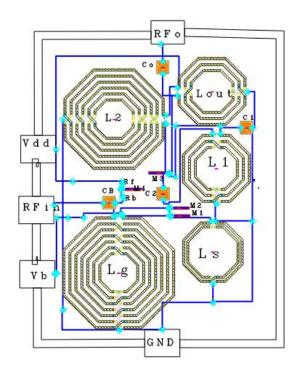

| Figure 4.42 | Layout of GPS CRLNA.                                                                | 68 |

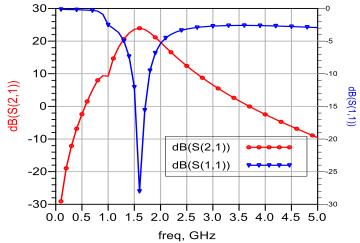

| Figure 4.43 | S21 and S11 simulation results of GPS CRLNA.                                        | 68 |

| Figure 4.44 | S12 and S22 simulation results of GPS CRLNA.                                        | 69 |

| Figure 4.45 | Noise Figure simulation results of GPS CRLNA.                                       | 69 |

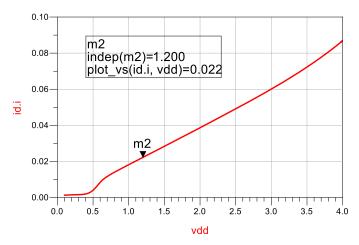

| Figure 4.46 | DC Simulation of GPS CRLNA.                                                         | 69 |

| Figure 4.47 | Harmonic simulation of GPS CRLNA.                                                   | 70 |

| Figure 4.48 | Stability factor simulation of CRLNA.                                               | 70 |

| Figure 4.49 | FOM of published and proposed GPS LNAs design.                                      | 71 |

| Figure 5.1  | EIRP Emission specified by the FCC.                                                 | 73 |

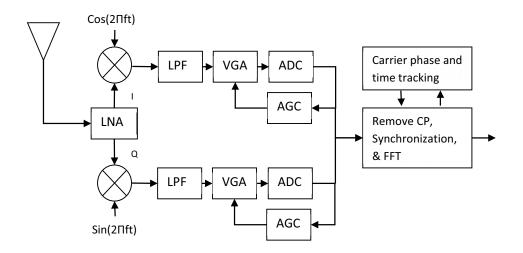

| Figure 5.2  | IR UWB Receiver architecture                                                        | 75 |

| Figure 5.3  | Multi Band proposed for the IEEE 802.15.3a standard                                 | 76 |

| Figure 5.4  | MB OFDM UWB receiver architecture                                                   | 76 |

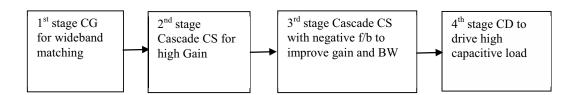

| Figure 5.5  | Different stages of proposed UWB LNA                                                | 77 |

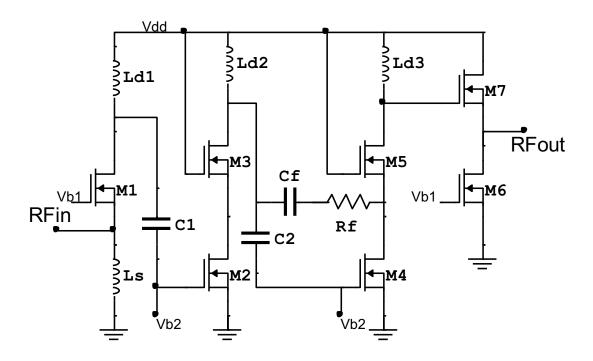

| Figure 5.6  | Circuit of proposed UWB LNA                                                         | 78 |

| Figure 5.7  | Common Gate input stage                                                             | 79 |

| Figure 5.8  | CG AC equivalent circuit                                                            | 79 |

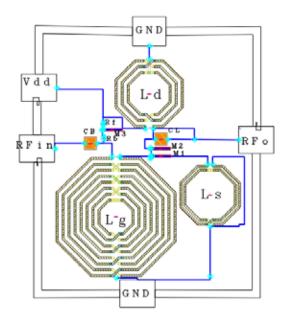

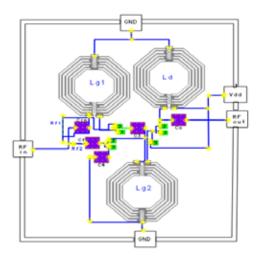

| Figure 5.9  | Layout of UWB LNA                                                                   | 81 |

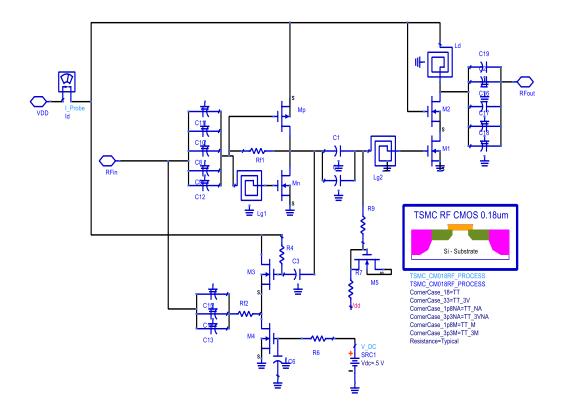

| Figure 5.10 | UWB LNA schematic                                                                   | 82 |

| Figure 5.11 | S <sub>21</sub> and S <sub>11</sub> simulation results of UWB LNA                   | 82 |

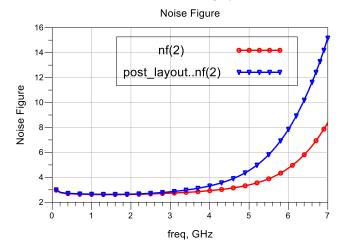

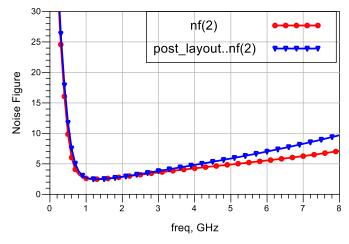

| Figure 5.12 | Noise Figure Simulation results of UWB LNA                                          | 83 |

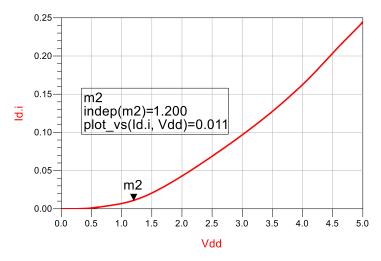

| Figure 5.13 | DC simulation result of UWB LNA                                                     | 83 |

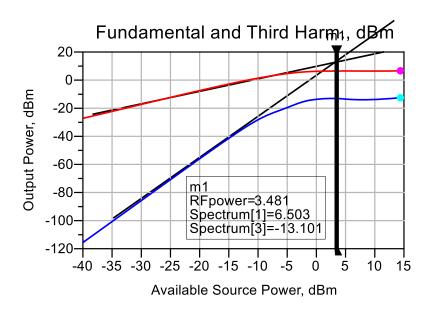

| Figure 5.14 | Harmonic simulation result of UWB LNA @ 6GHz frequency                              | 83 |

| Figure 5.15 | IIP3 versus frequency of UWB LNA                                                    | 84 |

| Figure 5.16 | Group Delay variation of UWB LNA.                                                   | 84 |

| Figure 5.17 | FOM Comparison of Proposed UWB LNA with published work                              | 85 |

| Figure 6.1  | NMOS/PMOS inverter structure                                                        | 88 |

| Figure 6.2  | Resistive feedback inverter wideband LNA schematic                                  | 90 |

| Figure 6.3  | $S_{21}$ and $S_{11}$ simulation results of resistive feedback inverter LNA $\dots$ | 92 |

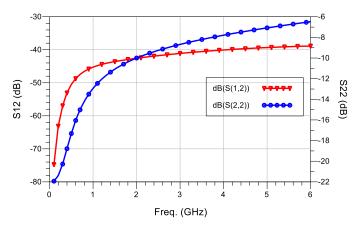

| Figure 6.4  | $S_{12}$ and $S_{22}$ simulation results of resistive feedback inverter LNA $\dots$ | 93 |

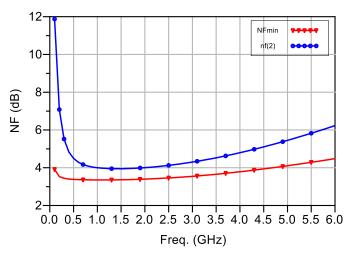

| Figure 6.5  | Noise Figure simulation results of resistive feedback inverter LNA                  | 93 |

| Figure 6.6  | DC simulation result of resistive feedback inverter LNA                         | 93  |

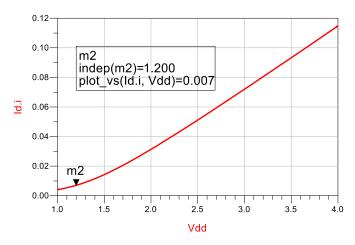

|-------------|---------------------------------------------------------------------------------|-----|

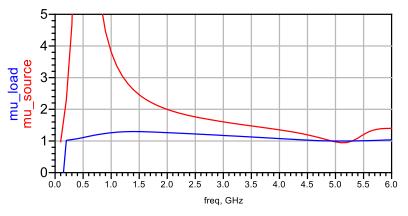

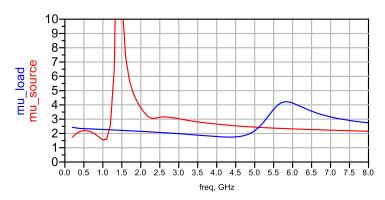

| Figure 6.7  | Stability simulation result of resistive feedback inverter LNA                  | 94  |

| Figure 6.8  | Resistive feedback inverter with gate inductor wideband LNA                     | 95  |

| Figure 6.9  | Resistive feedback inverter and its AC equivalent circuit                       | 95  |

| Figure 6.10 | Resistive feedback with gate inductor inverter structure and its AC             |     |

|             | equivalent circuits                                                             | 96  |

| Figure 6.11 | Pole splitting in S plane                                                       | 97  |

| Figure 6.12 | $S_{21}$ and $S_{11}$ simulation results of resistive feedback with Lg inverter |     |

|             | LNA                                                                             | 98  |

| Figure 6.13 | $S_{12}$ and $S_{22}$ simulation results of resistive feedback with Lg inverter |     |

|             | LNA                                                                             | 98  |

| Figure 6.14 | Noise Figure simulation result of resistive feedback with Lg inverter           |     |

|             | LNA                                                                             | 98  |

| Figure 6.15 | S <sub>11</sub> simulation results of with and without Lg resistive feedback    |     |

|             | inverter LNA                                                                    | 99  |

| Figure 6.16 | S <sub>21</sub> simulation results of with and without Lg resistive feedback    |     |

|             | inverter LNA                                                                    | 99  |

| Figure 6.17 | Resistive and CD feedback inverter wideband LNA schematic                       | 100 |

| Figure 6.18 | CS with common drain active feedback schematic                                  | 101 |

| Figure 6.19 | $S_{21}$ and $S_{11}$ simulation results of resistive and CD inverter feedback  |     |

|             | LNA                                                                             | 102 |

| Figure 6.20 | Noise Figure simulation result of resistive and CD feedback inerter             |     |

|             | LNA                                                                             | 102 |

| Figure 6.21 | DC simulation result of resistive and CD feedback inverter LNA                  | 103 |

| Figure 6.22 | Proposed highly linear multi standard wideband LNA schematic                    | 104 |

| Figure 6.23 | Layout of proposed highly linear multi standard wideband LNA                    | 105 |

| Figure 6.24 | Highly linear wideband LNA schematic                                            | 105 |

| Figure 6.25 | S <sub>21</sub> simulation result of highly linear wideband LNA                 | 106 |

| Figure 6.26 | S <sub>11</sub> simulation result of highly linear wideband LNA                 | 106 |

| Figure 6.27 | Noise figure simulation result of highly linear wideband LNA                    | 106 |

| Figure 6.28 | DC simulation result of highly linear wideband LNA                              | 107 |

| Figure 6.29 | Stability factor simulation result of highly linear wideband LNA                | 107 |

| Figure 6.30 | Harmonic simulation @4GHz result of highly linear wideband LNA                  | 107 |

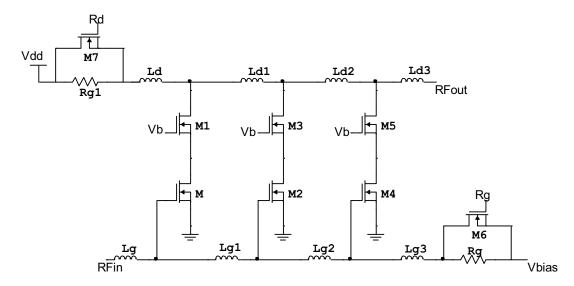

| Figure 6.31 | High power gain wideband LNA schematic                         | 109 |

|-------------|----------------------------------------------------------------|-----|

| Figure 6.32 | Layout of high power gain wideband LNA                         | 109 |

| Figure 6.33 | $S_{21}$ simulation result of high power gain wideband LNA     | 110 |

| Figure 6.34 | $S_{11}$ simulation results of high power gain wideband LNA    | 110 |

| Figure 6.35 | Noise Figure Simulation result of high power gain wideband LNA | 110 |

| Figure 6.36 | DC Simulation result of high power gain wideband LNA           | 111 |

| Figure 6.37 | Stability simulation of high power gain wideband LNA           | 111 |

| Figure 6.38 | Harmonic simulation @3GHz of high power gain wideband LNA      | 111 |

# **List of Tables**

| Table 2.1 | Sensitivity, SNR and Noise Figure specification of different standards |     |

|-----------|------------------------------------------------------------------------|-----|

|           | receiver                                                               | 15  |

| Table 2.2 | IIP3 requirement in different standards receiver                       | 20  |

| Table 3.1 | Summary of detail literature survey of the wideband LNA                | 35  |

| Table 4.1 | Bluetooth LNA component values and its function                        | 51  |

| Table 4.2 | Targeted and Achieved performance of Bluetooth LNA                     | 56  |

| Table 4.3 | CRLNA Design variables value and its function                          | 57  |

| Table 4.4 | Bluetooth LNAs performance comparisons with literature works           | 61  |

| Table 4.5 | Design variables value of GPS IDCS LNA                                 | 62  |

| Table 4.6 | GPS CRLNA Design variables value and its function                      | 66  |

| Table 4.7 | GPS LNAs achieved performance comparisons with literature works        | 70  |

| Table 5.1 | Components value of proposed UWB LNA design                            | 81  |

| Table 5.2 | IIP3 value at different frequency of UWB LNA                           | 84  |

| Table 5.3 | Compare results with published Wideband Low Noise Amplifier            | 86  |

| Table 6.1 | Sensitivity, linearity and Noise Figure specifications of different    |     |

|           | standards                                                              | 87  |

| Table 6.2 | Components value of resistive feedback inverter LNA                    | 92  |

| Table 6.3 | Components value of resistive feedback with Lg inverter LNA design     | 97  |

| Table 6.4 | Components value of resistive and CD feedback inverter LNA design      | 102 |

| Table 6.5 | Components value of proposed highly linear wideband LNA design         | 104 |

| Table 6.6 | IIP3 value of highly linear wideband LNA design at different           |     |

|           | frequency                                                              | 108 |

| Table 6.7 | Components value of high power gain wideband LNA                       | 108 |

| Table 6.8 | Comparison of designed wideband LNAs results with published work       | 113 |

| Table 6.9 | Wireless Standards                                                     | 114 |

#### CHAPTER 1

## Introduction

#### 1.1 Introduction

The computer will become the hub of a vast network of remote data stations and information banks feeding into the machine at a transmission rate of a billion or more bits of information a second.... Eventually, a global communications network handling voice, data and facsimile will instantly link man to machine—or machine to machine—by land, air, underwater, and space circuits.

—David Sarnoff, 1964

The demand of wireless communication applications push VLSI designer to continuous research in wireless transceiver RFICs design. Application of wireless communication is increasing exponentially. Different wireless standards like GSM, CDMA, UMTS, GPS, Wireless LAN (IEEE 802.11a/b/g), Bluetooth, ZigBee, LTE and WiMax are operate in different frequencies and having different modulation schemes. As per wireless communication users demand future smart phone should support all wireless standards with low power dissipation, less cost and compact size. Currently handsets have separate RF frontend and digital base band processing for each wireless standard which not only require larger silicon area but also consume more power. In order to reduce power dissipation, complex interfacing, cost and area requirement of smart phone, future wireless receiver should have single wideband high performance RF frontend to support all wireless communication standards. The LNA designing is most critical task in RF frontend and its performance impact in overall performance of RF receiver.

#### 1.2 Universal Receiver

All wireless standards receiver should integrate in single chip with hardware sharing and reusing as per future demand. The receiver which supports all wireless communication standards is known as universal receiver.

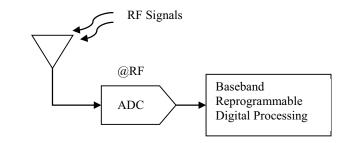

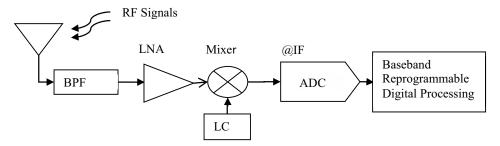

Ideal universal receiver architecture proposed by mitiola [1] is shown in Fig. 1.1. Implementation of ideal universal receiver for RF is still not reality because of it puts very tough design requirements of Analog to Digital Conversion (ADC) to process low amplitude RF signal. Designing of ADC for RF universal receiver is impossible task using current technology. Practical universal receiver architecture is incorporating Low Noise Amplifier (LNA) and mixer as shown in Fig. 1.2. Mixer is relaxed the speed performance requirement of the ADC by down conversion of frequency. An LNA relaxes dynamic range, noise and linearity performance requirements of the ADC, hence Low Noise Amplifier is essential to implement any RF receiver.

FIGURE 1.1: Ideal universal radio architecture.

FIGURE 1.2: Practical universal radio architecture.

Designing of the LNA for universal receiver is still a challenging task. At present multi standards receiver designs are dedicated to optimized for specific wireless standard and obtain best performance but at higher cost and more power consumption. The universal receiver has key advantages, such as reconfigurable, low complexity, low power dissipation and no image frequency as compare to super heterodyne receiver architecture.

Digital RF is another architecture in addition to universal receiver used for RF receiver [2]. In digital RF receiver architecture all tradition block such a mixer and filter are replaced by its digital counterpart. The main problem in implementation of digital RF receiver is its high speed sampling, which introduce more noise. Signal to Noise Ratio (SNR) of the input signals in the digital RF receiver need to increase for noise reduction. There for, the Low Noise Amplifier becomes essential component for universal and digital RF receiver. Still there is no receiver architecture for RF wireless communication that can eliminate the need of LNA.

Multi wireless standards receiver requires high power gain, low noise figure, high linearity and wideband input matching LNA. Overall receiver sensitivity depends on gain and Noise Figure (NF) performance of LNA, linearity of the system depends on transfer function and reverse isolation of the LNA. The designing of wideband LNA for universal receiver pose many challenges and it is emphasized in the thesis.

#### 1.3 Introduction of UWB System

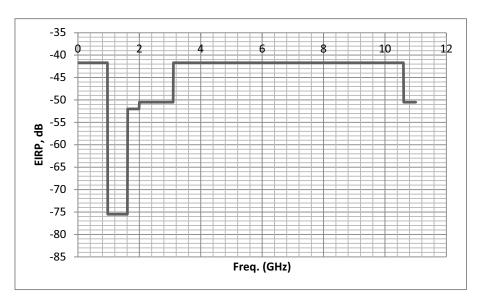

Federal Communications Commission (FCC) has approved ultra wideband (UWB) 3.1-10.6 GHz frequency band for commercial use in 2002 with restriction to transmit information using low power. Extremely wide bandwidth of UWB system provides high transmission channel capacity and less multi path fading. So it opens new frontier for wireless communication users. The UWB system is widely used in high data rate wireless communication, image penetration and high accuracy locating applications.

Despite all the favorable features of the UWB systems, serious challenges exist for the realization of 3.1-10.6 GHz wideband high power gain Low Noise Amplifier (LNA) for UWB RF frontend. FCC's limit transmitter power and due to addition path loss receiver receive low power signals. Process low power received signals UWB receiver requires high power gain and low noise figure wideband matching LNA. One of the objectives of this research work is analyzed and design high power gain 3.1-10.6 GHz UWB LNA for UWB receiver.

#### 1.4 The CMOS Technology

Before 1980s discrete components, such as transistors, resistors, capacitors and inductors were widely used to design RF receive circuits. The discrete design of RF receiver was bulky, expensive and poor performance. The advancement in VLSI technology has replaced discrete components based implementation of wireless receiver using RFIC. The Complementary Metal Oxide Semiconductor (CMOS) is advanced enough to implement any wireless communication applications system. The CMOS technology has low fabrication cost and high level of integration, so it is more attractive solution of RFIC. The realization of passive components like resistors, capacitors and inductors using CMOS will increase speed, reduce size and cost of RF receiver. 0.18µm RFCMOS technology is the targeted process for the work due to its low fabrication cost, good technology performance, good Ft (unity gain cutoff frequency) and good linearity. The unity gain cut off frequency of 0.18 µm RFCMOS technology is good enough to provide high gain up to 15 GHz frequency.

#### 1.5 Definition of the Problem

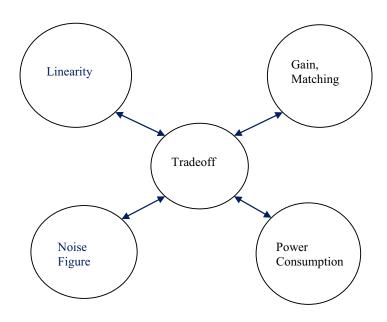

After the two decade of research in RFIC circuit designing, it is still challenging due to three factor (i) RFIC design require multidiscipline knowledge of the IC designing, microwave theory, transceiver architectures, communication theory, wireless standards, Random signals, CAD tools, Multiple access, and Signal Propagation. (ii) RF circuit design deal with tradeoffs of Gain, Power consumption, Noise, Linearity and Bandwidth (iii) the demand of high performance, low cost, low power and greater functionalities. These three challenging factors of RFIC design push VLSI researcher to do research in implement of RFIC.

Wireless communication applications are increased rapidly which leads to challenge wireless RF circuit's designer to design RFIC for next generation wireless communication receiver. Objective of this research work is to analyze, design and implementation of two narrowband LNAs for Bluetooth and Global Positioning System (GPS) receiver, three wideband LNAs for future multi standards universal and UWB receiver.

Due to FCC restriction on power transmission in use of UWB for commercial wireless applications require low noise high power gain receiver to amplify and process received weak signals. For this two approaches can be used to implement LNA for UWB receiver either multiple LNA chain for each band of UWB or

- single 3.1-10.6GHz wideband LNA. The second approach, 3.1-10.6GHz wideband LNA not only reduce silicon area requirement but also reduce power consumption. To improve performance of UWB system requires high power gain, low noise figure and wideband matching 3.1-10.6GHz wideband LNA.

- To support existing 2G and 3G GSM, UMTS, CDMA, Bluetooth, ZigBee, GPS, WLAN with future 4G LTE and WiMAX wireless communication standards requires high performance RF Frontend receiver. The performance of LNA decides overall performance of receiver. Next generation multi standard receiver will require 0.6-5.6GHz wideband, High gain, Low noise Figure, good linearity and wideband input matching LNA to support future wireless standards.

#### 1.6 Objective and Scope of the Work

The design of LNA for future universal receiver is still a challenging task. The next generation multi standards multi-mode wireless communication applications require high power gain, highly linear wideband RF front end. The implementation of multi-mode multi standard receiver using multi transceiver which not only requires larger silicon area but also consumes more power and it is not suitable for battery operated device. Universal radio receiver architecture has wideband transceiver, which support multi standards wireless communication applications and reduce silicon area and power consumption. Objective of this research work is to design wideband LNAs for next generation universal and UWB system receiver.

# 1.7 Original Contribution by the Thesis

Original contribution of the thesis is propose analyze, design of two narrowband LNAs for Bluetooth and GPS receiver and three wideband LNAs for multi standards next generation and UWB system receiver. All the LNAs are design using 0.18  $\mu$ m RFCMOS and simulate the designs using Advance Design System RF simulator tool.

The thesis contributes detailed analysis of input matching, gain and noise figure of inductive degenerate common source (IDCS) topology of Low Noise Amplifier (LNA). The Narrowband LNAs are designed using IDCS topology for Bluetooth

- and GPS receiver. Portable Bluetooth receiver LNA is designed using current reuse topology to reduce power consumption, which will improve battery lifetime.

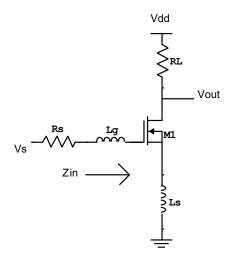

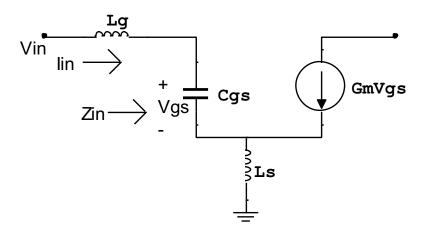

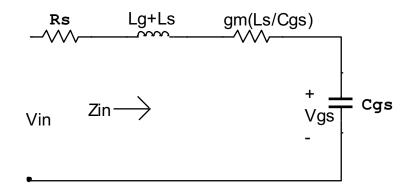

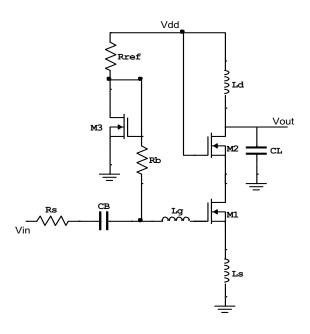

- In this research work, proposed high power gain 3.1-10.6 GHz UWB LNA for commercial applications. The first stage of proposed design is inductive source Common Gate (CG) for wideband matching. Input impedance and noise figure of CG are analyzed in detail and optimized the design for low noise figure. CG has low power gain which can be improved by using two cascade CS stages. To reduce noise in this design inductive load is used instead of resistive in each stage. The inductive load not only reduces noise but also increases gain by forming parallel tune circuit with next stage input capacitor. The bandwidth of this LNA is increased by resonating each output parallel tune circuit at different frequencies. The results shows proposed LNA design is highly suitable to increase performance of UWB receiver.

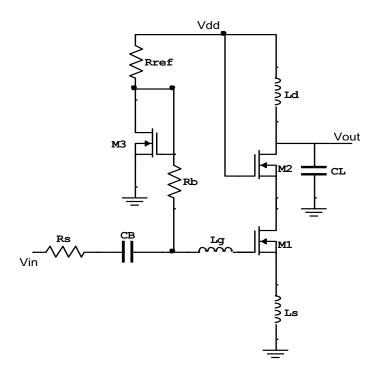

- The proposed 0.6-5.6GHz wideband LNA design has highly linear and high power gain to support multi standards future universal receiver. To support LTE and WiMAX 4G standards with existing GSM, CDMA, UMTS, Bluetooth, ZigBee and WLAN standards require 0.6-5.6 GHz wideband matching, high linearity, high gain and low noise figure receiver. Distortion cancellation analysis of NMOS/PMOS inverter structure carried outs, resulted as inverter structure provides good linearity. Analyzed input capacitance and efficiency factor of inverter structure amplifier and proposed solution to cancel the effect of input capacitance to improve gain at higher frequency. There is tradeoff between low noise figure and wideband matching in selection of feedback resistance value of resistive feedback inverter LNA. In the research propose, the design of LNA to relax tradeoff between low noise figure and wideband matching. The novel highly linear LNA design is based on common drain and resistive feedback inverter structure with series and shunt peaking inductors CS next stage for future mobile terminal.

The research work published in peer review international journals and IEEE internal conferences.

#### 1.8 Thesis Organization

Thesis is organized in seven different chapters including this introduction chapter 1.In Chapter 2, introduce the fundamental concepts of LNA. The S parameter and it use in two port network analysis is discussed. The different performance parameters of LNA relevant to receiver are introduced, such as impedance matching, noise figure, Power gain, harmonic distortion and stability.

In chapter 3, a wideband LNA state of art has been discussed. Different wideband topologies are analyzed in details with pros and cons. Each wideband topology performance parameters like input impedance, noise figure are analyzed in detail and tradeoff among them are discussed.

Chapter 4 covers the design steps of narrowband LNA using inductive source degenerate topology. The Bluetooth receiver narrowband LNAs are designed using inductive degenerate common source as well as current reuse topology. The Global Positioning System (GPS) requires high sensitive receiver to receive weak GPS signals. The chapter also covers design and simulation of narrowband LNAs for GPS receiver using IDCS and current reuse topology. The end of the chapter compares the proposed LNAs performance with published work.

Chapter 5 covers detailed analysis and designing of high power gain UWB LNA for UWB wireless applications. Input impedance and noise figure of Common Gate stage of the proposed UWB LNA design is analyzed. The LNA design is optimized for low noise figure. The proposed LNA is design using 0.18µm RFCMOS technology and the design simulated using Advanced Design System RF simulation tool. The simulation results show the design having wideband input matching, high power gain and low noise figure compare to published work.

Chapter 6 covers the detailed analysis of distortion cancellation of NMOS/PMOS inverter structure. The chapter covers analysis and design of gate inductor based LNA to improve gain and input matching at higher frequency. The complete analysis of resistive feedback NMOS/PMOS structure LNA is carried out in this chapter. The chapter covers analysis, design and simulation of Common Drain (CD) active and resistive feedback inverter structure. Performance parameters of CD active feedback inverter LNA design is analyzed. At the end of the chapter proposed, design and simulate highly linear multiple negative

feedback inverter structure with inductive series and shunt peaking CS LNA topology for the next generation universal receiver to support existing 2G, 3G along with coming 4G wireless standards. Also, in the chapter covers design and simulation of high power gain LNA for base station universal receiver. The chapter ends with comparison of achieved performance of proposed LNAs with published work.

In last chapter 7 Concludes the work with major contributions and also discusses future scope to extend the work.

### **CHAPTER 2**

### **LNA Fundamentals**

#### 2.1 S Parameters

At RF frequency S parameter is widely used to describe two port networks instead of Z, Y, ABCD and H parameters. The S parameters are defined in terms of incident and reflected waves. As shown in Fig. 2.1  $a_1$  and  $b_1$  are incident and reflected waves of port1 respectively and  $a_2$  and  $b_2$  are incident and reflected waves of port2 respectively.

FIGURE 2.1: Two port network.

The  $b_1$  and  $b_2$  are dependent on the  $a_1$  and  $a_2$  and relationship between the incidents and reflected waves are described using (2.1) and (2.2).

$$b_1 = S_{11}a_1 + S_{12}a_2 \tag{2.1}$$

$$b_2 = S_{21}a_1 + S_{22}a_2 (2.2)$$

Equation (2.3) shows matrix representation of (2.1) and (2.2).

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11} S_{12} \\ S_{21} S_{22} \end{bmatrix} . \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(2.3)

The S parameters are easily understood by (2.1) and (2.2). The  $S_{11}$  is defined as

$$S_{11} = \frac{b_1}{a_1} | at \ a_2 = 0 \tag{2.4}$$

$S_{11}$  shows how much of  $a_1$  is reflected back to  $b_1$ .  $S_{11}$  shows measure of input matching for maximum power transfer. If reflected power  $b_1$  is 0, means all input power is transferred. The value of  $S_{11}$  is 0 or in logarithmic value  $-\infty$  which shows perfect matching. The practical value of  $S_{11}$  should be as low as possible for maximum power transfer and below -10 dB is preferable. The  $S_{12}$  is defined as

$$S_{12} = \frac{b_1}{a_2} | at \ a_1 = 0 \tag{2.5}$$

Value of  $S_{12}$  shows how much power is transferred from port2 to port1.  $S_{12}$  measure how good is the isolation between port1 and port2, and its value should be as low as possible for better isolation from port2 to port1. The  $S_{21}$  is defined as

$$S_{21} = \frac{b_2}{a_1} | at \ a_2 = 0 \tag{2.6}$$

$S_{21}$  is ratio between output power at port2 and input power at port1. It shows power gain of two port network. Similarly  $S_{22}$  is defined as

$$S_{22} = \frac{b_2}{a_2} | at \ a_1 = 0 \tag{2.7}$$

$S_{22}$  measures output port matching. Value of  $S_{22}$  should be as low as possible for better port2 matching with load so that it can transfer maximum power to load.

A good amplifier should have  $S_{11}$ ,  $S_{22}$  and  $S_{12}$  low and  $S_{21}$  high.  $S_{11}$  is used to measure the input match and  $S_{21}$  is used to measure power gain of the LNA.

The stability of the two port network is analyzed using S parameters. The necessary condition for stability is expressed in terms of S parameters as (2.8).

$$K = \frac{1 - |S_{22}|^2 - |S_{11}|^2 + |\Delta_S|^2}{2|S_{12}S_{21}|} > 1 \tag{2.8}$$

Where,  $\Delta_s = S_{11}S_{22} - S_{12}S_{21}$ . Two port network is stable if it satisfy condition given in (2.9)

$$||\Delta_s|^2 - L| + L > 1 \tag{2.9}$$

Where,  $L = |S_{12}S_{21}| + \frac{|S_{11}|^2 + |S_{22}|^2}{2}$

### 2.2 Low Noise Amplifier (LNA) Performance Parameters

Major performance parameters of the LNA are:

- Noise Figure (NF)

- $\triangleright$  Power Gain (S<sub>21</sub>) and Input matching (S<sub>11</sub>)

- Linearity (IIP3)

- Power consumption

- > Stability

#### 2.2.1 Noise Performance

The Noise performance of two port network is measured using Noise Factor (F). The noise factor is defined as the ratio of the total output noise power to the output noise due to input source. If the Noise Factor is expressed in decibels it is called the Noise Figure (NF).

$$SNR = \frac{P_{\text{signal}}}{P_{\text{noise}}} \tag{2.10}$$

$$F = \frac{\frac{P_{si}}{P_{ni}}}{\frac{P_{so}}{P_{no}}}$$

(2.11)

$$NF = 10 \log(F) \tag{2.12}$$

Where,  $P_{si}$  is input signal power,  $P_{ni}$  is the input noise power,  $P_{so}$  is the output signal power and  $P_{no}$  is the output noise power. Overall noise figure of multistage amplifier receiver is express as

$$NF_{tot} = 1 + (NF_1 - 1) + \frac{NF_2 - 1}{A_{p1}} + \dots + \frac{NF_m - 1}{A_{p1} \dots A_{p(m-1)}}$$

(2.13)

Equation 2.13 is also known as Friis formula which is named after the Danish-American electrical engineer Harald T. Friis. The first amplifier stage of receiver contribute major portion of overall noise. The first amplifier stage of receiver is known as Low Noise Amplifier (LNA). This is the rationale behind why the first stage of amplifier has to a low noise figure as possible.

**NOISE DEFINITION:** Noise arises in electronic circuits as a random variable and is non-deterministic. Noise generated in circuit is due to nature of the materials or by external interferences. Signal degrades due to noise. So it is needed to carefully analyze and develop method to minimized effect of noise on signals. In following section, the main noise sources present in circuit are described. [3] [4].

**THERMAL NOISE:** Thermal noise in circuits is due to the random motion of electrons. Thermal noise signal power is expressed as (2.14)

$$P = kT\Delta f \tag{2.14}$$

Where k is the Boltzmann's constant, T is the temperature in Kelvin, and  $\Delta f$  is the bandwidth in Hz of the system. Thermal noise voltage generated in resistor is modeled as (2.15).

$$\overline{V_{th}^2} = 4kTR\Delta f \tag{2.15}$$

Where, R is resistance value in ohm. Similarly thermal noise current produce in resistor is expressed using (2.16).

$$\overline{I_{th}^2} = \frac{4kT\Delta f}{R} \tag{2.16}$$

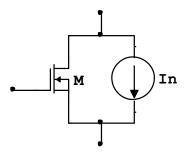

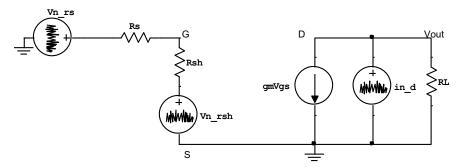

MOSFET also exhibit thermal noise due to the carrier motion in the channel. This noise is modeled by putting current source in parallel MOSFET with conducting channel as shown in Fig. 2.2. This noise current modeled when device operate in triode mode as (2.17). [5]

$$\overline{I_n^2} = 4kT\gamma g_{d0}\Delta f \tag{2.17}$$

Where,  $\gamma$  is the excess noise parameter and  $g_{d0}$  is the drain to source conductance for  $V_{DS} = 0$ . When MOSFET operate in saturation mode channel thermal noise current modeled as it shown in (2.18). [6]

$$\overline{I_n^2} = 4kT\gamma g_m \Delta f \tag{2.18}$$

Where,  $\gamma = 2/3$  [7] for long channel device, For short-channel and submicron MOSFETS,  $\gamma$  has higher values, in a range between 1 and 3 [8].

FIGURE 2.2: MOSFET channel thermal noise representation.

**DISTRIBUTED GATE RESISTANCE NOISE:** Another source of noise in MOSFET is thermal noise generated by distributed gate resistance. This gate resistance is dependent on the MOSFET geometry. The gate resistance for a single polysilicon gate finger, connected on both sides is expressed as (2.19) [9].

$$R_G = \frac{1}{12}\rho_{sh}\frac{W}{L} + \frac{\rho_{con}}{WL} \tag{2.19}$$

Where,  $\rho_{sh}$  is silicide sheet resistance, W and L is the width and length of the MOSFET channel and  $\rho_{con}$  is silicide to polysilicon contact resistance.

FIGURE 2.3: Equivalent noise model for gate resistance.

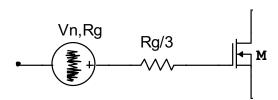

In Fig. 2.3 shows equivalent noise model of gate resistor where  $R_G/3$  is equivalent gate resistance and Vn,Rg is equivalent gate noise voltage [4] [10].

Effective silicide sheet resistance can be reduce by using multi fingers gate design [9], [11] and it decrease gate resistance thermal noise. If value of power spectral density of this noise is very less than channel thermal noise, then it can be neglected.

$$4kT\frac{R_G}{3} \ll \frac{4kT\gamma}{g_m} \tag{2.20}$$

**FLICKER NOISE:** The flicker noise in MOSFET is due to a physical phenomenon, and it is unpredictable. It is related with the interface between the silicon substrate (Si) and gate oxide (Sio2). The flicker noise is due to random fluctuation of carriers in the channel, caused by trapping and release of carriers in the Si and SiO2 interface. Flicker noise is proportional to 1/

f, so it is neglected at higher frequencies. It is model by a flicker noise voltage source in series with the gate. The flicker noise is modeled using (2.21).

$$\overline{V_{nf}^2} = \frac{k_f}{c_{ox}WLf} \tag{2.21}$$

Where,  $k_f$  is a process dependent constant, and  $C_{ox}$ , W, and L are the gate oxide capacitance per unit area, width, and length of the MOSFET respectively. For p-channel devices  $k_f$  is lower than for n-channel devices, and thus PMOS transistors have less flicker noise.

**SHOT NOISE:** Shot noise is caused by fluctuation of the current that crosses a pn junction potential barrier. The diffusion of charge carriers is random and cause different speed of carriers. The shot noise defined as (2.22).

$$\overline{I_{ns}^2} = 2qI_{DC} \tag{2.22}$$

Shot noise is originating the fluctuation of current around an average value. Where, q is the electron charge and  $I_{DC}$  is the DC current. Shot noise is more significant in bipolar junction transistors compared to MOSFET because both emitter and collector currents are sources of shot noise. In MOSFETs, the DC gate leakage current contributes shot noise and it is usually very small and in most cases it can be neglected.

The sensitivity of a receiver is defined based on what minimum signal power can be processed by receiver. Receiver sensitivity is determined from minimum signal to noise ratio (SNR), Noise figure and noise power.

$$P_{sens} = SNR_{Rxmin} + P_{n.s} + NF_{Rx} \tag{2.23}$$

where,  $P_{sens}$ ,  $SNR_{Rxmin}$ ,  $P_{n,s}$  and  $NF_{Rx}$  are receiver power sensitivity in terms of dBm, minimum SNR in dB, source noise power in dBm and the noise figure in dB of the receiver respectively. If sensitivity, transmitted power and path loss knows maximum distance of communication take place can be find. Therefore minimum noise figure of receiver is desired to improve sensitivity of receiver. The LNA first stage of receiver should have low noise figure in order to reduce overall noise figure and better sensitivity of receiver. Most of Communication standards required SNR, sensitivity and NF are specified in Table 2.1. NF below 4dB of LNA is expected in most of communication standards.

|                         | GSM  | WCDMA | Bluetooth | RFID | WLAN | LTE  | WiMAX |

|-------------------------|------|-------|-----------|------|------|------|-------|

| P <sub>sens</sub> (dBm) | -102 | -117  | -70       | -70  | -65  | -102 | -65   |

| SNR<br>(dB)             | 9    | 5.2   | 21        | 11.6 | 28   | 8    | 24    |

| NF<br>(dB)              | 9    | 9     | 23        | 39   | 7.5  | 9    | 7     |

TABLE 2.1: Sensitivity, SNR and Noise Figure specification of different standards receiver.

### 2.2.2 Power Gain and Impedance Matching

LNA is the first amplifier stage in receiver to amplify weak signals incoming from antenna. For maximum power transfer from output of antenna to input of LNA require input impedance of LNA match to the output impedance of antenna. If impedance does not match, signal is reflected back and cause noise. To maximize power transfer input impedance matching is very important parameter in LNA design.  $S_{11}$  of two port network S parameter indicate ratio between reflected signal powers to the input signal power at port 1.  $S_{11}$  is measure in dB and below -10 dB of  $S_{11}$  is desired. -10dB of  $S_{11}$  mean 10% of total input power reflected back. Similarly, output impedance of LNA should match with next stage input impedance for maximized transfer of amplified output power of LNA to next stage input. Output impedance matching is measured by  $S_{22}$  of S parameter. Other design performance parameter is Power gain ( $S_{21}$ ), it should be as high as possible to increase strength of weak received signals.

#### 2.2.3 Linearity

In the LNA design linearity is another importance parameter to be considered when receiving weak input signals with strong interfering signals. Strong interference signals is produce cross modulation and blocking undesired inter modulation distortion in poor linear system.

**DEFINITION OF NONLINEARITY:** For memoryless linear system input output relationship is defined as (2.24)

$$y(t) = \alpha x(t) \tag{2.24}$$

Where  $\alpha$  is a function of time if system is time variant or a constant for time invariant system. For memoryless nonlinear system input/output relationship is define as (2.25) [12].

$$y(t) = \alpha_0 + \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t) + \cdots,$$

(2.25)

**HARMONIC DISTORTION NONLINEARITY:** If x(t) = Acos(wt) sinusoidal is applied to nonlinear system, then it produces output as

$$y(t) = \alpha_1 A \cos \omega t + \alpha_2 A^2 \cos^2 \omega t + \alpha_3 A^3 \cos^3 \omega t \tag{2.26}$$

$$= \alpha_1 A \cos \omega t + \frac{\alpha_2 A^2}{2} (1 + \cos 2\omega t) + \frac{\alpha_3 A^3}{4} (3\cos \omega t + \cos 3\omega t)$$

(2.27)

$$= \frac{\alpha_2 A^2}{2} + (\alpha_1 A + \frac{3\alpha_3 A^3}{4})\cos \omega t + \frac{\alpha_2 A^2}{2}(\cos 2\omega t) + \frac{\alpha_3 A^3}{4}(\cos 3\omega t)$$

(2.28)

In (2.28) the first term on right-hand side is a dc quantity arising from second-order nonlinearity, the second term is fundamental component with multiplication gain factor, the third term is second harmonic distortion and the fourth term is the third harmonics distortion. Harmonic distortion is not a major nonlinearity because suppose amplifier operating at 2.4 GHz produce second harmonic at 4.8 GHz which is out off band of filter [12].

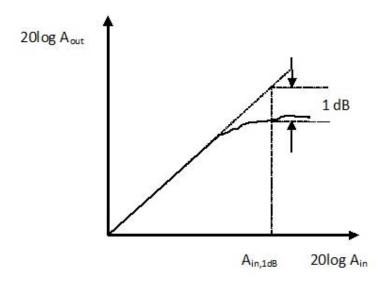

**GAIN COMPRESSION NONLINEARITY:** Formulation of harmonics shows gain experienced by Acos(wt) is equal to  $(\alpha_1 + \frac{3\alpha_3 A^2}{4})$  and hence varies noticeably as A becomes larger. If  $\alpha 1\alpha 3 < 0$  which make decreasing gain as an A increase. This effect can be measured with 1dB Gain Compression point, which can be define as the input power level of signal which causes the gain to drop by 1dB from its interpolated extended value as shown in figure 2.4. If plotted in logarithmic scale as a function of input power at a 1dB compression point output power fall 1dB from its ideal value [12].

The 1 dB compression point can be calculated by equating compressed gain to 1dB less than the ideal gain

$$20\log(\alpha_1 + \frac{3\alpha_3 A^2}{4}) = 20\log(\alpha_1) - 1dB$$

(2.29)

Gain A at this point is called A<sub>in, 1dB</sub> and it can be found from solving (2.29)

$$A_{in,1dB} = \sqrt{0.145 \left| \frac{\alpha_1}{\alpha_3} \right|} \tag{2.30}$$

The 1 dB compression means 10% reduction in gain and it's widely used to characterize RF systems.

FIGURE 2.4: 1dB compression point.

Another adverse effect from compression occurs if strong interfering signal goes along with the received signal. In the time domain, the weak desired signal is superimposed on the strong interfering signal. Due to that, gain of receiver is reduced by the large excursion produced by the interferer even though the desired signal itself is small and is called as "desensitization". This phenomenon lowers the signal to noise ratio (SNR) at the output and proves critical even if the signal contains no amplitude information [12].

For the qualitatively measure desensitization, let us assume  $A_1 \cos(w_1 t)$  is desire signal and  $A_2 \cos(w_2 t)$  is interferer signal so input to amplifier is  $x(t) = A_1 \cos(w_1 t) + A_2 \cos(w_2 t)$ Nonlinear system output appear as

$$y(t) = \left(\alpha_1 + \frac{3}{4}\alpha_3 A_1^2 + \frac{3}{2}\alpha_3 A_2^2\right) A_1 \cos \omega_1 t + \cdots$$

(2.31)

For  $A_1 \ll A_2$ , this reduce to

$$y(t) = \left(\alpha_1 + \frac{3}{2}\alpha_3 A_2^2\right) A_1 \cos \omega_1 t + \cdots$$

(2.32)

Thus, the gain experienced by the desired signal is equal to  $\left(\alpha_1 + \frac{3}{2}\alpha_3A_2^2\right)$ , a decreasing function of  $A_2$  if  $\alpha_1\alpha_3 < 0$ . Larger value of  $A_2$  make gain drop to zero, this condition is called signal blocking. In RF design the term blocking signal or blocker refers to interferers that desensitize a circuit even if they do not reduce the gain to zero [12].

**CROSS MODULATION NONLINEARITY:** When weak desire signal with large interfering signal pass through poor linear system, then it transfer modulation in desire signal from interfere this phenomena is called cross modulation. To understand cross modulation effect, let us take modulated interferer signal  $A_2(1 + mcos\omega_m t)cos\omega_2 t$  with desire signal  $A_2(cos\omega_1 t)$  passing through a nonlinear system produce output

$$y(t) = \left[\alpha_1 + \frac{3}{2}\alpha_3 A_2^2 \left(1 + \frac{m^2}{2} + \frac{m^2}{2}\cos 2\omega_m t + 2m\cos \omega_m t\right)\right] A_1 \cos \omega_1 t + \cdots$$

(2.33)

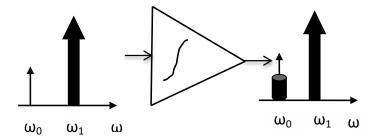

The (2.33) says that desired signal suffer from amplitude modulation at  $\omega_m$  and  $2\omega_m$  frequency. Cross modulation nonlinearity effect is graphically illustrate in Fig. 2.5.

FIGURE 2.5: Cross modulation nonlinearity effect.

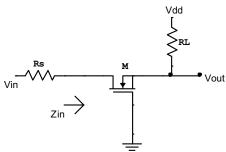

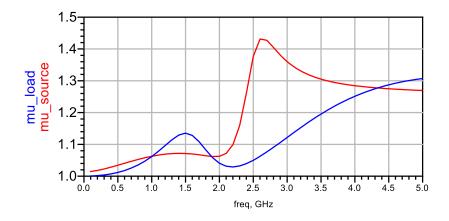

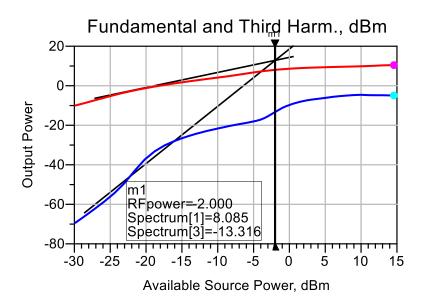

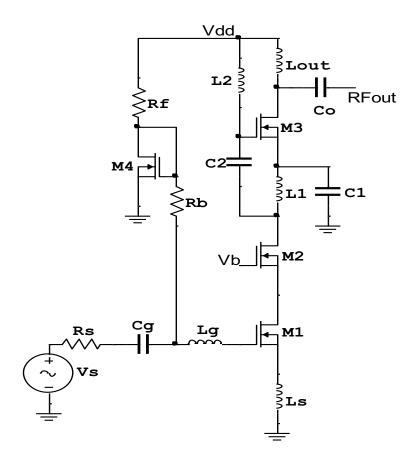

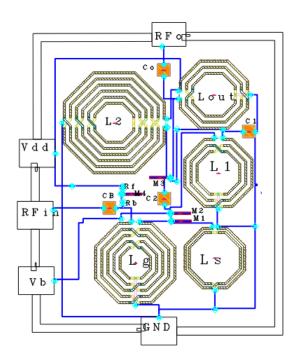

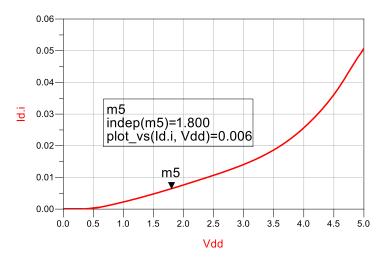

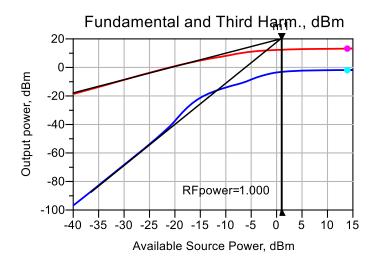

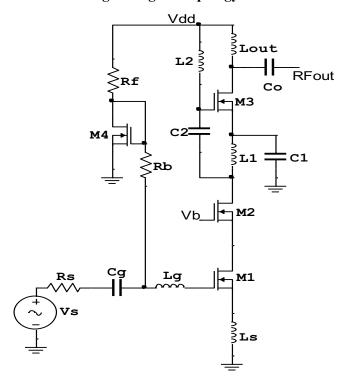

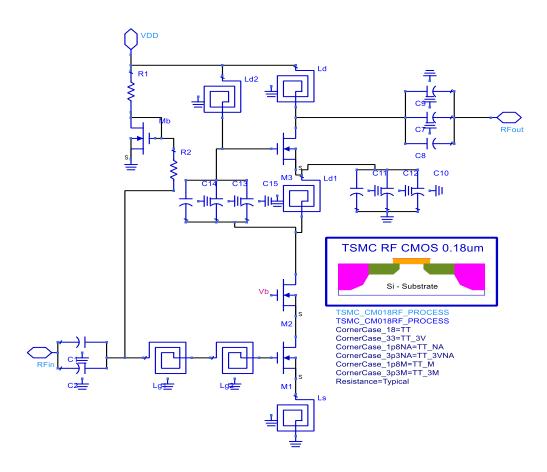

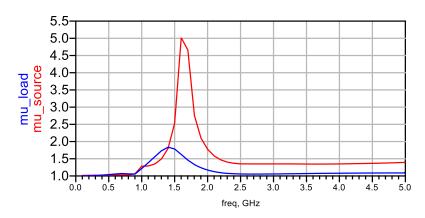

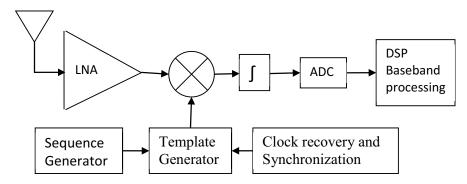

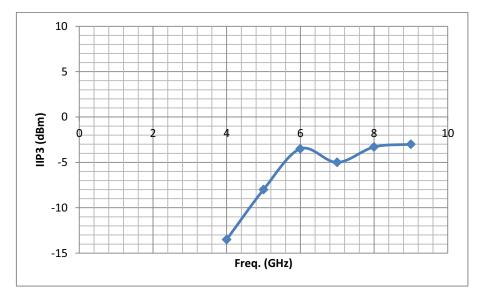

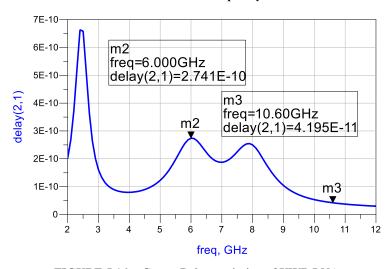

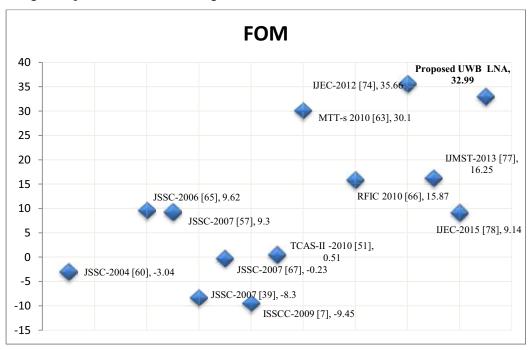

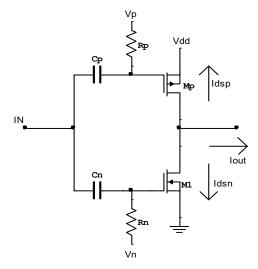

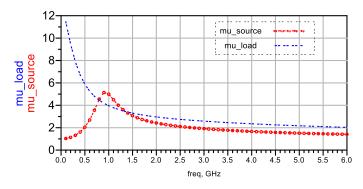

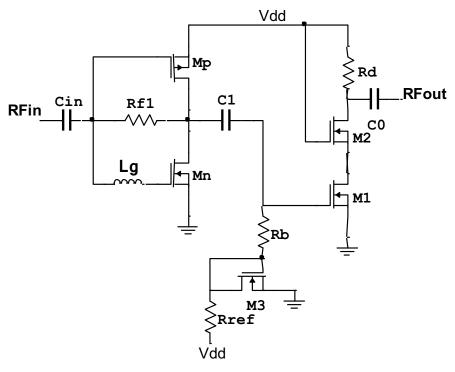

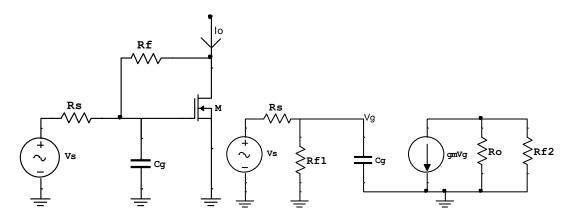

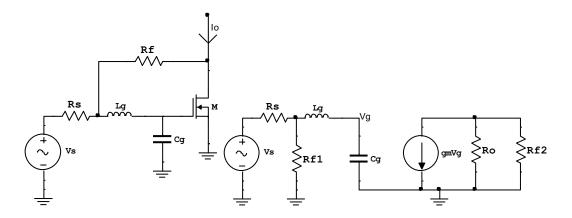

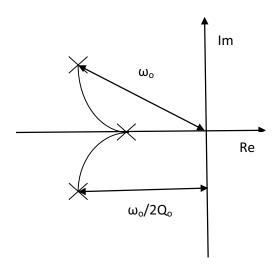

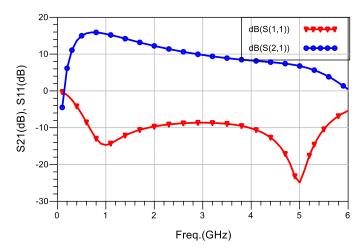

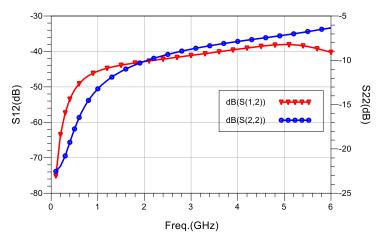

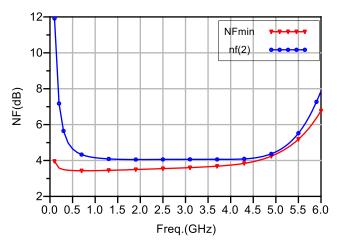

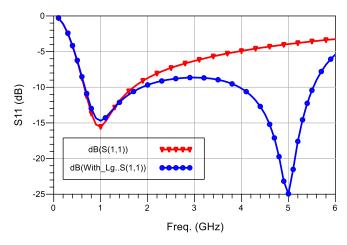

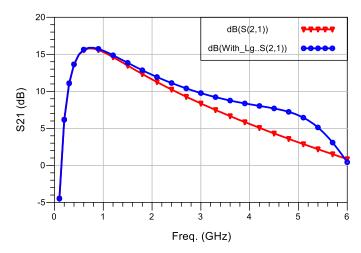

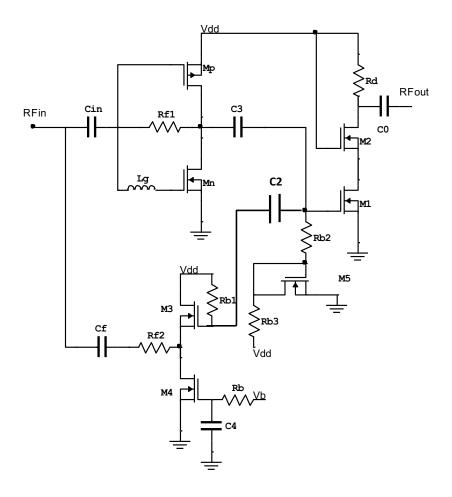

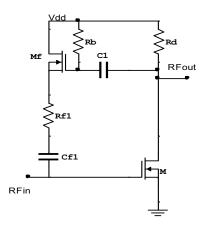

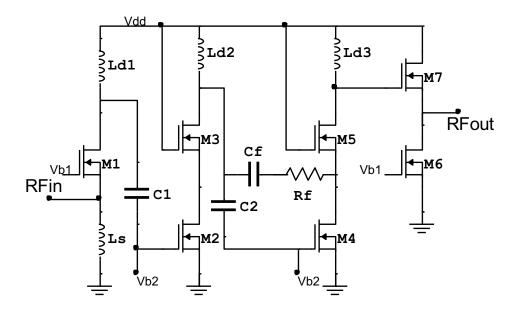

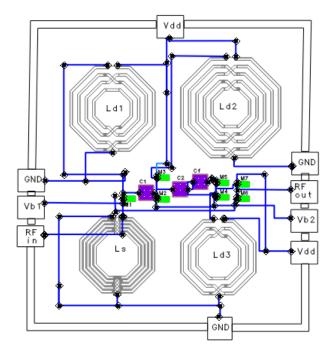

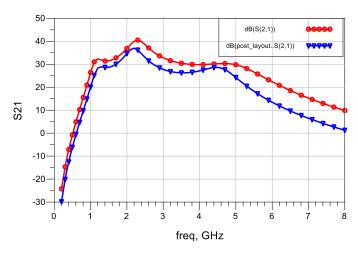

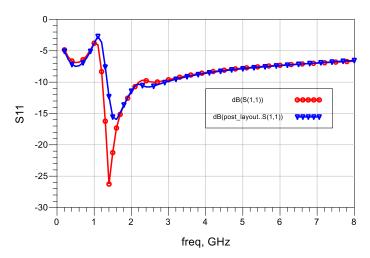

All above nonlinearity effect consider only single signal. Another nonlinearity effect occurs if two interferes accompany the desired signal. If two interferers of different frequency  $\omega_1$  and  $\omega_2$  are applied to a nonlinear system then produce output generally contain components that are not the harmonics of  $\omega_1$  and  $\omega_2$  frequencies called intermodulation. To understand intermodulation let take  $x(t) = A_1 cos \omega_1 t + A_2 cos \omega_2 t$  combination interferers signals as input to any nonlinear system. Output is